# THE ATV Compendium

Mike Wooding, G6IQM

## **BRITISH AMATEUR TELEVISION CLUB**

a suggestion of the second

### **BRITISH AMATEUR TELEVISION CLUB**

# THE ATV COMPENDIUM

Mike Wooding, G6IQM

### ACKNOWLEDGEMENTS

The author wishes to express his gratitude to the following for their major contributions to this book:

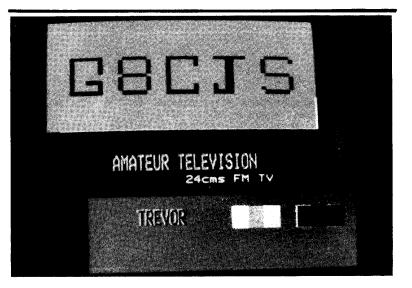

Trevor Brown, G8CJS who supplied most of the circuits in the video section.

Bob Platts, G802P for the technical details of the 10GHz transceiver.

John Wood, G3YQC for the Universal Sync Generator.

Peter Delaney, G8KZG for the Digital Framestore.

Acknowledgement is also made to the following for information and assistance....

Klaus Hirschelmann, DJ700. G.Wehrhahn, DD9DUK. Bill Brown, WB8ELK. Steve Mitchell, G8JMJ. Chris Smith. David Stone.

.....and also to the authors of works to which reference has been made, to the editors of other publications whose permission has been granted for reproduction of information, and to all those who have given advice and encouragement during the compilation of this book.

For information regarding membership of the BATC please contact Dave Lawton GØANO, Membership Secretary, 'Grenehurst', Pinewood Road, High Wycombe, Bucks. HP12 4DD, enclosing a stamped addressed envelope.

(C) British Amateur television Club 1989

Extracts from this book may be reproduced for publication by nonprofitmaking amateur organisations, on condition that full credit is given to the BRITISH AMATEUR TELEVISION CLUB. The use of material for other purposes is at the discretion of the author.

First edition.

First printing March 1989.

Wooding, Mike: The British Amateur Television Club The ATV Compendium

ISBN 0-9513779-1-4

#### VIDEO CIRCUITS

| DUAL-STANDARD PATT  | ERN GENERATOR | <br> | 5 |

|---------------------|---------------|------|---|

| FOUR-INPUT VISION   | SWITCHER      | <br> | 6 |

| ELECTRONIC VISION : | SELECTOR      | <br> | 8 |

| FADE TO BLACK       |               |      |   |

| SUPERIMPOSING CAPT  |               |      |   |

| ELECTRONIC AMATEUR  |               |      |   |

| VIDEO DISPLAY GENER | RATOR         | <br> |   |

| TELETEXT PATTERN GI | ENERATOR      | <br> |   |

| DUAL-STANDARD COLOR | UR CODER      | <br> |   |

| VIDEO DISTRIBUTION  | AMPLIFIER     | <br> |   |

#### SPECIAL PROJECTS

| A DIGITAL FRAMESTORE       |                                         | 36 |

|----------------------------|-----------------------------------------|----|

| A UNIVERSAL SYNC GENERATOR | •••••••                                 | 53 |

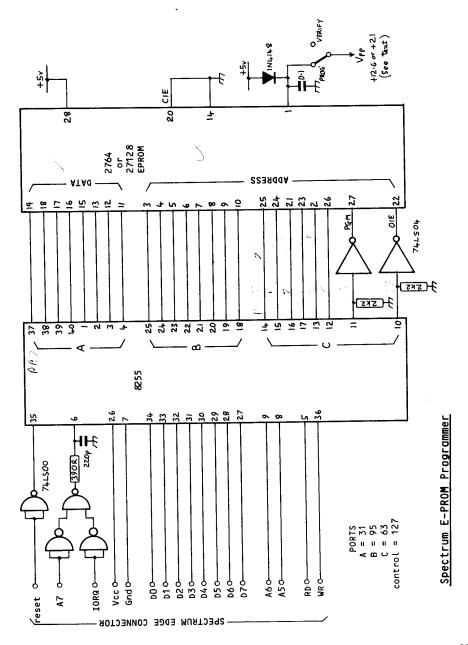

| SPECTRUM E-PROM PROGRAMMER | • • • • • • • • • • • • • • • • • • • • | 64 |

#### R.F. PROJECTS

| Ga | aAs | FET   | CONVI  | ERTER  | FOR  | 24CM | AMATEUR | TRANSMITTER | <br>68 |

|----|-----|-------|--------|--------|------|------|---------|-------------|--------|

| A  | 240 | CM FI | VTA N  | TRANS  | SMIT | TER  |         |             | <br>74 |

| A  | 3CM | ATN   | / TRAI | VSCEIV | ER . |      |         |             | <br>83 |

### FOREWORD

For something approaching the past decade the BATC has been publishing handbooks, dealing exclusively with the world of Amateus Television. These publications have proved to be very popular with the membership throughout the years, prompting the club to reprint and update the material from time to time.

The last handbook the Club produced was the 'Slow Scan Companion', the first publication of its kind in the United Kingdom totally dedicated to Slow Scan Television. This handbook marked another landmark in the Club's history, in that it was the first of our publications to feature a full colour cover.

The ATV Compendium does not break any bounds in the club's publication record, but I hope it will serve to inform those interested in Amateur Television, particularly those of you involved in home construction. I have tried to include projects that include the use of 'state-ofthe-art' techniques and devices, without precluding those who do not own sophisticated test equipment or have degrees in mechanical engineering.

There is one large omission from this book that I am sure will not go unnoticed, this is the lack of a 70cm section. Although this was certainly not intentional when I started, it soon transpired that the amount of material coming in for other topics, particularly 3cm, coupled with the absolute lack of anything new for 70cm, meant that for the first time an Amateur Television handbook without a section for the seventy sentimentalists would be the outcome. Also, with the vast commitment of time necessary by all involved with the production of a book like this, coupled with the economics of publishing books with greater page counts, had any material for 70cm been available I would have been in a difficult situation deciding what to leave out.

However, with the pressure being placed on 70cm these days, from inside the amateur world as well as outside, perhaps the time has come for us to place the emphasis on the higher bands. It is certainly true to say that working in amateur TV on the higher bands is exciting, offering the opportunity for experimentation in the true amateur split. There is a lot of work to be done in the area of wideband FM and high definition television, and I feel sure that the amateur world has a lot to offer the professionals, as has certainly been the case in the past.

Finally, I wish to offer my personal thanks to all those mentioned in the acknowledgements for their help. Also, special thanks go to John Wood GYQC for his help with all the artwork, editorial advice and support during what appears to have been a very long year, and to Trever Brown GRCJS for his support.

I hope that you find this book interesting, informative and above all, useful.

Mike Wooding G6IQM.....Editor.

4

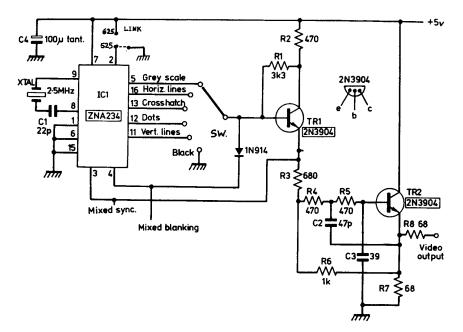

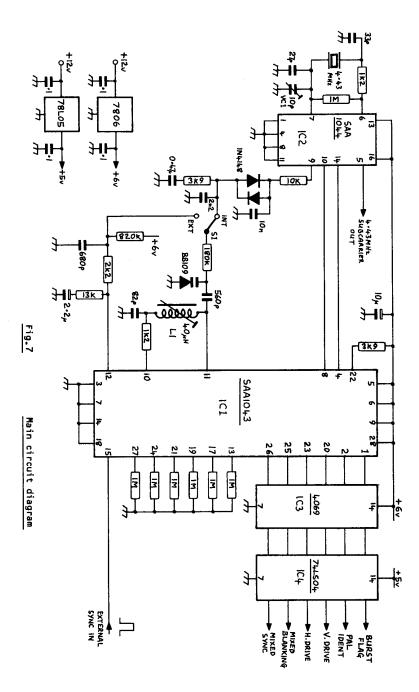

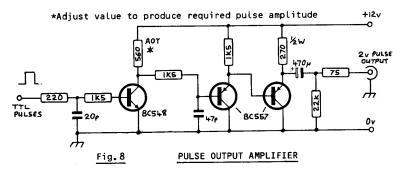

### DUAL-STANDARD PATTERN GENERATOR

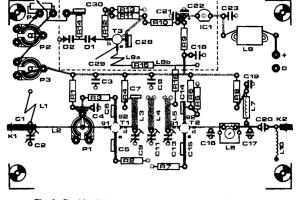

A useful aid in the ATV shack is a pattern generator, useful for setting up monitors, transmitters, VCR's etc. This circuit is built around the Ferranti ZNA234 television sync and pattern generator IC. The patterns available are grey-scale, horizontal lines, grille, dots and vertical lines. The grey-scale pattern is a descending one (ie: white at the left, through grey, to black at the right) rather than the more usual ascending one. This does not however affect its use as a test waveform.

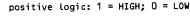

The ZNA234 is a multi-standard device in that the line frequency is set externally by an appropriate crystal. For 625 lines the crystal frequency should be 2.5MHz and for 525 lines 2.18MHz. The number of lines per frame is set by the voltage condition on pin-2 of the chip, connecting it to +5 volts sets the frame rate for the 625 line standard, connecting it to 0 volts for 525 lines.

Transistors TR1 and TR2 provide the necessary buffering of the signal from TTL levels to present a composite 75-ohm video output. Mixed sync and blanking are available from pins 3 and 4 respectively at TTL levels, for driving additional equipment if required.

There is no printed circuit board available for this unit, but it can be simply constructed using Vero-board. As with the simple pattern generator described elsewhere no special attention needs to be paid to the layout of the components.

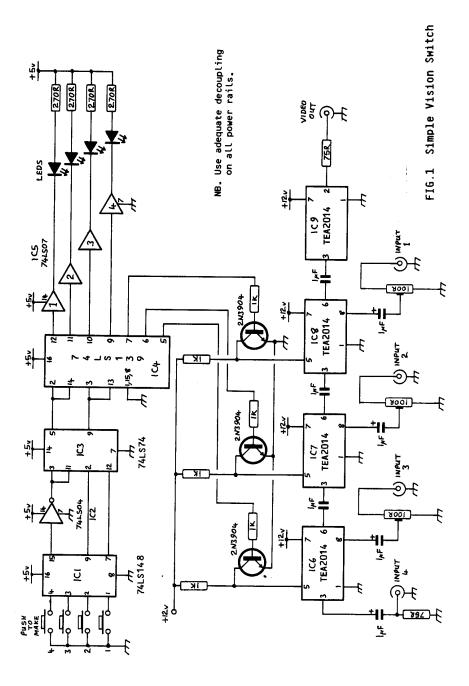

### FOUR-INPUT VISION SWITCHER

An alternate circuit for a four-input vision switcher is described here using the TEA2014 device. This device features one vide... changeover switch and a separate non-switched output, in an 8-pin duel in-line package. In order, therefore, to provide our four input unit three of these devices are required.

#### CIRCUIT DESCRIPTION

The inputs are selected by pressing an appropriate push-button which should be a momentary type with an in-built LED. The circuit gives priority to the right-hand button (number 4) should more than one be pressed at once.

When a button is operated IC1, an 8-to-3 line encoder, generates a 2-bit code representing that button. This code is stored in a dual D-type (IC3) which is first cleared by IC1, thus ensuring that the correct code is stored. An inverter (IC2) is required between the output from the encoder at pin-15 and the clock inputs on the D-type, pins-3 and 11.

The code is then passed to a 74LS139 dual 1-of-4 decoder (IC4), which has the inputs to both halves paralleled together. One set of outputs from the decoder is used to switch on the LED's in the push-buttons and the other set used to control the vision switches. IC5's gates are used to buffer the decoder outputs and source the supply for the LED's in the push-buttons. Transistors are required to shift the voltage level from the TTL output of the decoder to the higher voltage required by the switching IC's.

The actual switching is carried out by the TEA2014 IC's (IC's 6 to 9) which are custom-built analogue vision switches. Each has two inputs; one via pin 3 having unity gain and the other via pin-8 having a gain of 2. To overcome the probability of non-standard video levels being presented to the switches, each input is via a 100 ohm potentiometer to allow all the input levels to be equalised at 1 volt p-p.

#### CONSTRUCTION

A printed circuit board has not been made available for this project as it is only offered as an alternative to the colour vision selector described elsewhere in this book. However, by carefully laying out the components on a piece of Vero-board a suitable unit could be built. Try to avoid crossing any video lines with others, and avoid placing the output adjacent to any input line. The push-buttons are numbered one to four on the circuit diagram with number four having the highest priority, and so on in reverse order down to number one. The power requirement is 12 volts, with the on-board 7805 regulator supplying the 5 volt rail for the logic. A suitable keyboard rocker switch is available from RS Components (Electromail) stock no: 337-374 (red LED) or 337-380 (green LED).

As suggested before, for a really 'professional' effect, the Fade-to-Black unit described elsewhere in this book should be installed between the switcher and the transmitter for smoother changeovers.

7

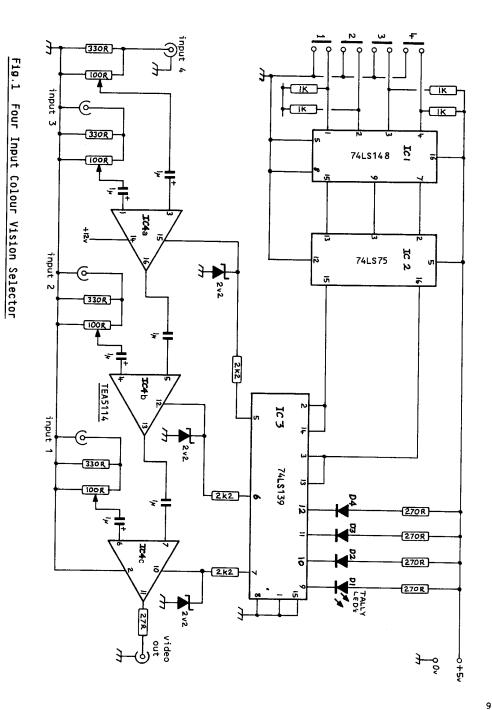

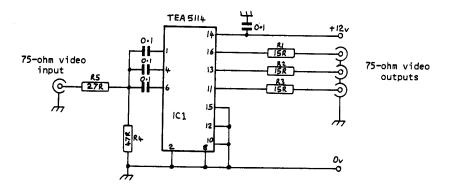

### ELECTRONIC VISION SELECTOR

The electronic vision selector is a very useful piece of equipment in the shack. With a multitudinous array of vision sources available to the modern amateur, such as cameras, computers, caption generators, VCR's etc., the method of changing plugs and sockets to select sources is no longer very satisfactory. The circuit described here offers a simple and practical way of effecting changes between four vision sources. Switching is not field sequential.

The unit is based on the Thomson TEA5114 custom built analogue video switch. This device contains three separate changeover switches and a fast blanking switch. Each of the switches within the device features a stage gain of two, thus in this circuit each of the inputs will have differing sensitivities, which can be accomodated by the gain controls. Low level video sources less than 1 volt should be applied to inputs 1 or 2 in order to benefit from the maximum gain of the cascaded switches.

#### CIRCUIT DESCRIPTION

The switcher provides four inputs and uses simple non-latching push-buttons to select sources. A tally LED is also provided for each input, which is switched on whenever the input is selected. The push-button commands are coded into a two-bit code by the 74LS148 Priority Encoder, this ensures that if two or more buttons are pressed at the same time the higher number button takes priority. The code is then latched into the 74LS75 and stored there until another button is pressed, as well as being routed to both halves of the 74LS139 Dual Decoder. One set of decoded outputs is used to drive the tally LED's and the other to control the TEA5114 switching. Voltage level adjustment between the outputs of the decoder and the control inputs of the switches is achieved by the Zener diode and 1K resistor. The inputs have an impedance of 75 ohms, and each has a 100-ohm gain control in order to balance the sources to provide a 1 volt p-p output into a 75 ohm load.

#### **LONSTRUCTION**

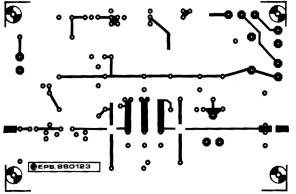

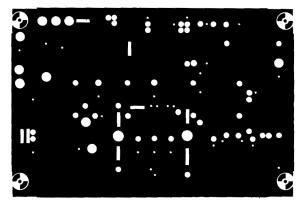

A pre-drilled printed circuit board is available from BATC Members' Services, this has a ground plane on the component side. Hefore fitting any components this ground plane should be removed from around the holes for components that do not connect to ground, using a small drill or Vero tool. The push-buttons as numbered on the circuit diagram give number four the highest priority and number one the lowest in the switching order. These switches may be either mounted direct onto the PCB, or remotely onto a front panel. Provision is also made on the PCB for the four 330-ohm resistors that pad the input down to 75-ohms, if remote input sockets are used these are best mounted at the sockets. A suitable keyboard rocker switch is available from RS Components (Electromail) stock no: 337-374 (red LED) or 337-380 (green LED.

It is suggested that for a really 'professional' effect, a Fade-to-Black unit be installed between the switcher and the transmitter, so as to give smooth transitions from one source to another. A circuit for such a unit is included elsewhere in this book.

, i

### FADE TO BLACK

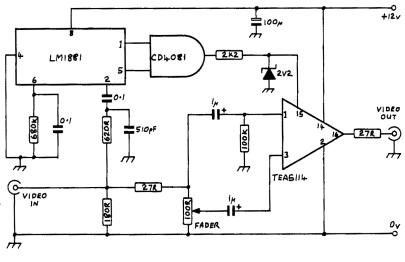

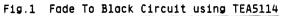

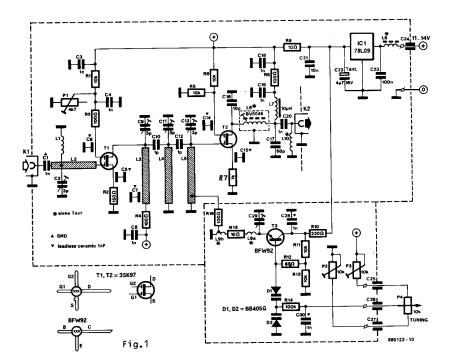

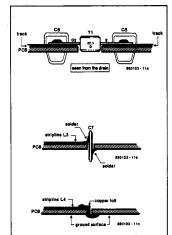

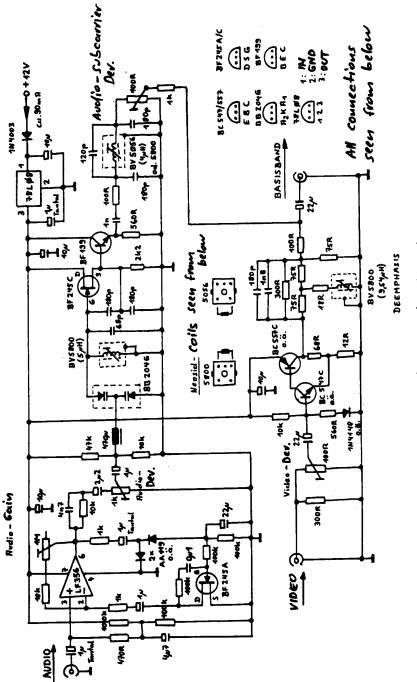

In order to effect a smooth changeover from one video source to another, the video should ideally be faded to black whilst the switching takes place. However, if the composite video source is simply faded down the sync pulses are also lost, and the resultant changeover suffers from loss of sync until the up-fade video signal is strong enough to lock the picture. Consequently, what is required is a unit that will fade the video but maintain the syncs. The two circuits described here do just that. In Fig.1 is shown a circuit using the TEA5114 device, and in Fig.2 using a TEA2014.

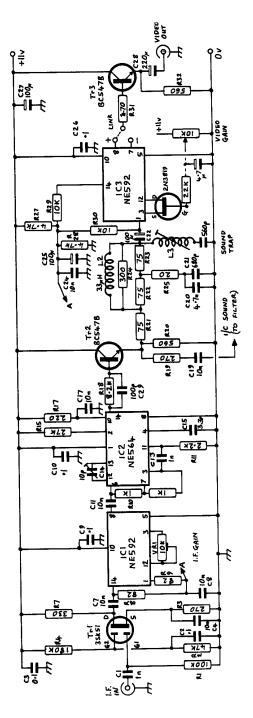

#### CIRCUIT DESCRIPTION

The incoming video signal is fed to the LM1881 Sync Separator IC, which extracts the sync pulses and the burst gate (if colour is being used). These two signals are then gated together by the TTL (74LS00) gate in Fig.1 and by the C-Mos (CD4081) gate in Fig.2. The logic signal at the output of the 74LS00 is inverted by TR1 (BC107) and fed to the switch control input. In Fig.2 the output from the C-Mos gate is too high for the control input of the TEA5114 video switch, so a 2.2K resistor and 2v2 Zener diode are incorporated to limit this to 2.5 volts.

The input video signal is also routed to the fader control, the output of which is fed to the normally open input of the video switch. The video is further routed to the normally closed input of the switch. During normal operation, without a fade, the video switch toggles between its two inputs, changing over from the input on pin-1 (pin-3 Fig.2) to that on pin-3 (pin-8 Fig.2) whenever the extracted sync control voltage is not present, and changing back again when it is. This toggling action is very fast and causes no disruption to the picture as the changeover actually occurs during the blanking period.

When the input video is faded down, during the time the switch is routed to the faded input (ie: between sync pulse trains) black level is routed to the output. However, during the sync pulse intervals the control voltage is again present and the switch changes to the non-faded input, thus presenting sync pulses and burst to the output. The end result of this is to give an output waveform containing normal sync and burst, but without any video information.

#### CONSTRUCTION

Due to the simplicity of the circuits, printed circuit boards have not been made available. The units can be easily built onto pieces of Vero-board and mounted directly onto the fader, if required. No particular attention need be paid to the positioning of the components. A single 12 volt power rail is all that is required.

NOTE: Early samples of the TEA5114 showed differences in the voltage levels of black level clamps at each input. This was overcome by adding the 100K resistor at pin-1. This has removed the problem in all units built so far, but if the problem persists a micro switch operated by the fader when in the non-fade position grounding pin-15 of the TEA5114 should be added. This would prevent the toggling action from taking place when no fade is present.

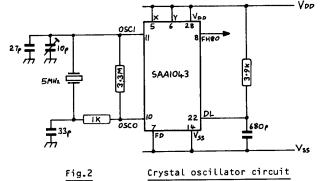

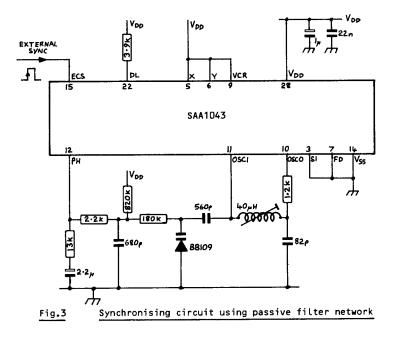

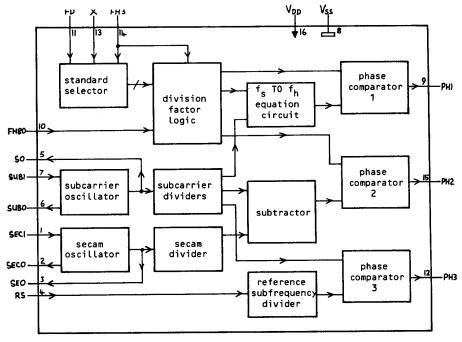

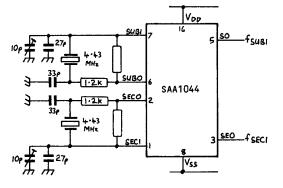

#### Fig.2 Fade To Black circuit using TEA2014

#### THE AMATEUR TV COMPENDIUM

11

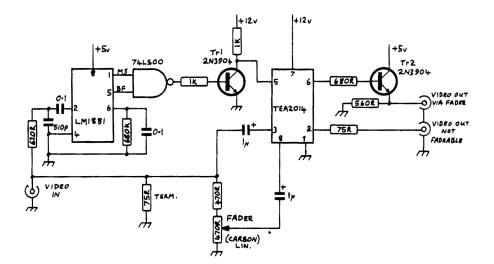

### SUPERIMPOSING CAPTION GENERATOR

The circuit described here is a character generator that will superimpose its caption onto any composite video signal. The unit works at both 525 and 625 line standards without any adjustment or circuit changes. The display consists of one line of fourteen characters which should be enough for your call sign and name or locator details. The circuit requires a composite video input signal to which it will synchronise. This is then inset in the form of a black box with white characters inside. The character fonts are stored in an E-Prom which has to be programmed with call sign and station details. Two video outputs are provided; one containing the inlaid caption and the other without. The display can be located at either the top of the picture or in the middle, alternatively it can be made to repeat several times down the screen.

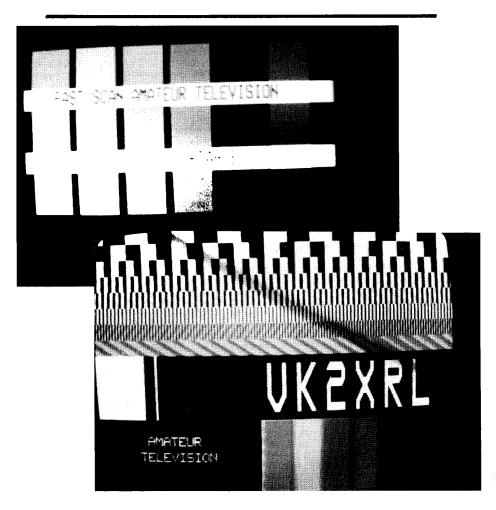

#### CIRCUIT

A basic block diagram is shown in Fig.1 and the circuit in Fig.2. Incoming video is fed to an LM1881 sync separator IC (IC8) which strips off the video and routes the sync information to the dot clock oscillator IC1. This oscillator runs at approximately two hundred times line frequency, and is synchronous to the incoming signal because it is stopped and restarted at the commencement of each scanning line. The dot clock is used to advance the column counter (IC3a), which generates an address that is incremented across the line and used to drive IC6, an 8-to-1 line data selector. IC6 scans across the data outputs of the E-Prom (IC5) and outputs a data stream to the data latch IC7a. This data stream represents the series of dots making up the top row of the first character.

The character counter IC4a is then advanced by the dot clock and with it the E-PROM address bus. IC6 now scans the E-PROM for the data information for the top row of the second character and sends the information to the data latch. This process is repeated until all fourteen characters have been scanned. The dot clock is stopped and restarted by the incoming sync information signalling the next scanning line. The row address counter IC4b is clocked by the incoming line sync and steps the E-PROM address bus through to the information for the next row of the characters, and the reading process repeated for the second row of each character. This entire process is repeated until all the character information has been read from the E-Prom. IC3b is the row counter and is advanced after each display. Switch S1 enables the counter to determine which lines are to be blanked out thus allowing the characters to be superimposed.

Data latch IC7 is required to clean up the dot stream and remove any false information from the ripple counters. The latch is clocked by the dot clock and its output routed to the video switch IC9. The characters are superimposed onto the through video by creating a 'black box' into which the characters are inserted. The black box is produced by clocking the video switch with a signal derived from the character row counter IC3b. When the TEA2014 is switched the character information is inserted into that picture line instead of the through video, thus building up a complete picture with the character information superimposed onto the video.

#### <u>CONSTRUCTION</u>

As with most of the projects in this book a printed circuit board is available from Members Services, please refer to your latest copy of CQ-TV for details. All the logic IC's should be 'LS' types, and are better mounted in good quality sockets. The E-PROM type shown in the circuit diagram is a 2716, however, the PCB has been designed to accommodate the larger 2732 and 2764 types. To facilitate this pin-23 has been left floating, for 2716 a solder bridge to the +5v pad should be fitted, for the other devices a solder bridge to ground. E-PROM types 2716 and 2732 should be fitted at the bottom of the socket, leaving locations 1, 2, 27 and 28 unused.

The video input requires terminating in 75-ohms. this has not been catered for on the PCB as some stations may require to switch it in or out to allow equipment to be looped together.

The connections for switch SW1 are brought out to solder pads at the edge of the board, as are the connections for RV1. These leads will be carrying signals at TTL levels and should not be longer than eight inches. this would allow connections to the front panel of an enclosure to be made.

The sync separator chips may be available from Members Services, please check your current copy of CQ-TV, alternatively, they are available from Farnell Electronics at the address shown below. Programmed E-PROMS are available from BATC Members Services, please quote the call sign and name or locator required when ordering.

The only setting-up required is the level of the superimposed characters, which is achieved by adjusting RV1 until the desired balance is obtained between the characters and the through video. The regulated power supply should be 12 to 15 volts and be capable of delivering 500mA.

Farnell Electronic Components, Canal Road, Leeds LS12 2TU. Tel: 0532 63611

Fig. 2 Video Character Generator

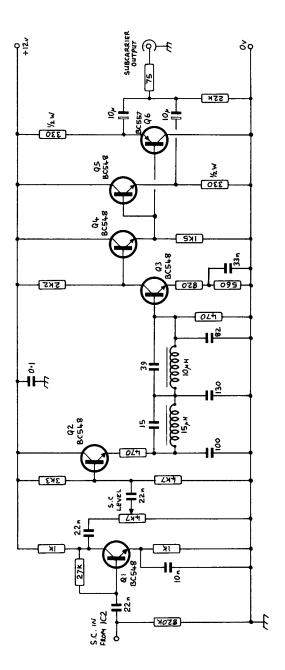

### ELECTRONIC AMATEUR TEST CARD

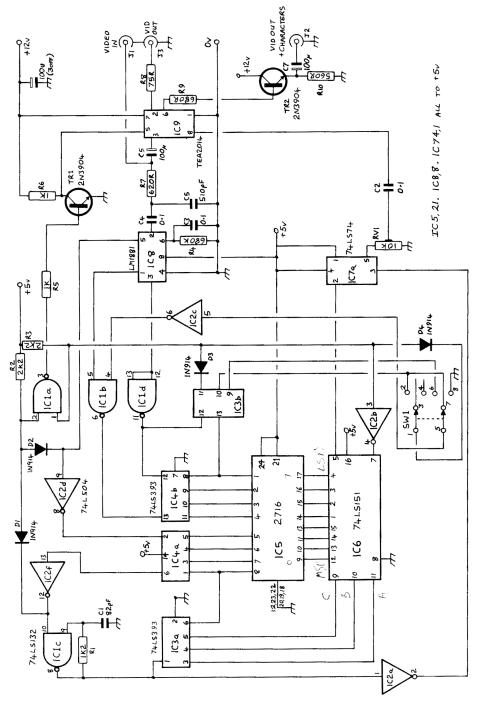

The electronic test card generator described here is based on the original design which appeared in Radio and Electronics World in July 1983. This circuit encompasses all the patterns provided by the two simple circuits described elsewhere in this book, plus extra important test signals to enable the correct setting of equipment. The test card has the added advantage of providing station identification and of being in colour. The colour content can be coded to the correct format for either the PAL or NTSC systems, and the whole unit requires only a single 12 volt supply. The pattern information, call sign and station details are held in a 2732 type E-Prom which is read by the logic circuitry of the generator. A pre-drilled printed circuit board is available from BATC Members Services, the E-PROMs are available with a choice of several different patterns from the Worthing Repeater Group (see advertisements in CQ-TV).

As stated the test card pattern has all the features of the other generators in the one pattern and these include:

- 1) Grille pattern to provide a rough linearity check on the monitor scans.

- Black rectangle within white to test the low frequency response, and white needle pulse to test for reflections.

- 3) 150KHz square wave to test transient response.

- 4) Up to eight bold characters for your callsign.

- 5) Multiburst bandwidth response test, producing 6uS bursts of 0.5, 1.0, 1.5, 2.0, 2.5 and 4.0MHz.

- 6) Colour bars to check the performance of a receiver decoder and the colour performance of any other units in the path, such as video switches, modulators, receivers and transmitters.

- Two lines of up to twenty characters for your QTH, shack details or other message.

- Optional BATC logo just to show that you are a member of the World's leading ATV organisation.

#### <u>CIRCUIT</u>

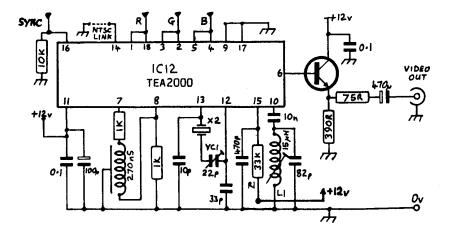

All the circuit timings are derived from a crystal oscillator (x1) which runs at 7.781MHz for 525 line working and 8MHz for 625. The oscillator uses two logic gates (IC2) biased as amplifiers, and this provides the video dot rate. The clock also drives the counter IC1 where it is divided down to 1 and 2MHz, the outputs from the counter provide the character clock and control signals.

The 1MHz clock drives the address counters IC3 and IC4, which are incremented for each character cell on the display for the 64 character row addresses. In each character cycle the address of the character is latched through a multiplexer into IC5, IC6 and IC7. The character corresponding to this address is read from the E-PROM (IC8) multiplexed, and then latched back into the E-PROM address along with the character scan line number from the address counter. This address gives the character number and scan line number for the character generator, which is also contained within the E-PROM.

The data output then forms the dot pattern which is converted into serial form by shift register IC9, and routed to the video circuitry. If when the character is read from the E-Prom the data bit is set, then the dot pattern when read is latched by IC10 instead of the shift register IC9. The output from IC10 is then used to control the colour coder chip IC12, reset the address counters and generate synchronisation pulses.

The reset pulse is used to return the address counter to zero at the end of each frame. Because of this the number of lines per frame is controlled by the E-PROM, thus it is necessary to program each E-PROM with both a 525 and a 625 test pattern. To select which pattern is required it is simply necessary to alter the logic state on A12 at pin-2 of the E-PROM, grounding the pin will select the 625 card, connecting it to +5 volts will select the 525 one. A PCB pad is provided at pin-2 of the E-PROM to enable this selection to be made easily.

The colour coder is contained within a single chip the TEA2000. This device is capable of encoding to NTSC or PAL standards by either grounding pin-14 for NTSC, or leaving it 'floating' for PAL. The crystal connected to pin-13 (x2) needs to be twice the frequency of the colour subcarrier, ie:8.867MHz for PAL and 7.1276MHz for NTSC. L1 should be adjusted for maximum subcarrier and the burst position may need altering between standards, this is done by changing the value of R1. The delay line at pin-8 should be a 270nS type (Philips V8470 270nS/900-ohm), as found in domestic TV sets.

The three D-A signals are multiplexed with the black and white signal in a quad 2-line to 1-line multiplexer (IC11). The resulting RGB signals are fed to the colour encoder IC12. The coded output is taken from pin-6 and is buffered by a simple video amplifier circuit providing a composite video output at 1 volt p-p across 75-ohms.

#### CONSTRUCTION

The pre-drilled PCB makes construction quite easy. Ensure that all the through-board wire links are soldered on both sides, as well as any components and IC leads that connect to both sides. Fit the correct frequency crystal for the standard you require and use good quality components throughout. The link at pin-2 of the E-PROM should be set for the test card required, as should the link at pin-14 of the coder for the system standard. The coder is quickly set up; adjust L1 for the maximum level of subcarrier and VC1 for correct locking of the colours (subcarrier frequency).

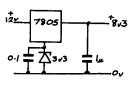

The 12-volt supply rail should be adequately regulated and be capable of supplying of the order of 500mA, all the logic circuitry is supplied from the on-board 7805 regulator. A heatsink should be fitted to the regulator device, this may be an on-board type but consideration must be given to the quite considerable heat generated when mounting the unit in a cabinet. It may be more suitable to mount the 7805 device off the board on a separate heatsink and feed the regulated +5 volts back to the circuit.

For details of ordering the PCB and E-PROMS please refer to the Member's Services and Worthing & District Repeater Group advertisements respectively in your current copy of CQ-TV.

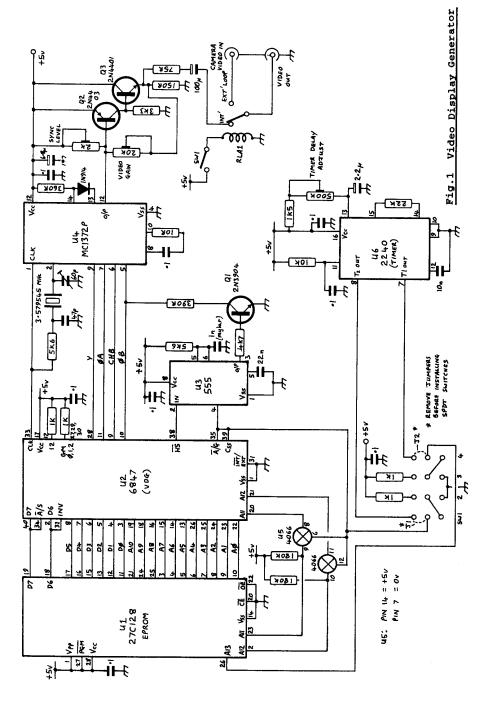

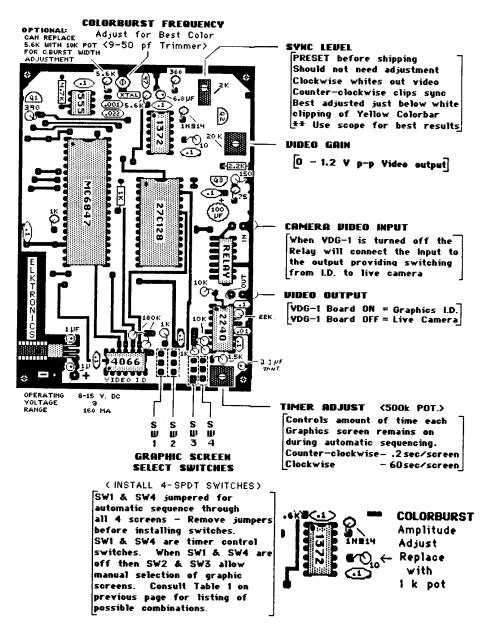

### VIDEO DISPLAY GENERATOR

This project has been included in the handbook specifically for our American members. The unit is designed to work to the 525 line NTSC standard, and as such is not suitable for use outside the USA.

The Elektronics VDG-1 Video ID board is a self contained module that will produce a quick source of computer video upon applying power. Four computer generated graphics screens are stored in a 27C128 E-PROM, two high-resolution screens and two colour bar patterns are available. These screens are located within different areas of the E-PROM's memory and are selected by controlling several address lines by means of four single-pole/double-throw switches wired to positions SW1 to SW4 on the printed circuit board. The output from the unit is standard 525 line NTSC at a level of 1 volt peak-to-peak, which can be connected direct to your ATV transmitter input, video monitor or video recorder. There is also a video relay in the circuit which routes live video through when the power is turned off. То identify your transmission, or for use as a test pattern, just turn on the ID board and the relay will switch from the through video to the generated picture. Finally, an automatic sequencer/timer featured in the circuit allows you to sequence through all four screens, or several combinations of two screens, varying from 0.2 seconds per screen up to a maximum of one minute per screen.

#### CIRCUIT DESCRIPTION

The circuit diagram of the unit is shown in Fig.1 The clock frequency to drive the 6847 Video Display Generator (VDG) IC is derived from a 3.579545MHz crystal, using part of the MC1327P IC as an oscillator. The VDG then generates all of the signals necessary to produce a video waveform. The computer graphics information stored in the 27C128 E-PROM is accessed by the VDG to produce the desired graphics screen. In combination with the control signals from the VDG the MC1372P functions as a colour/video mixer which adds in the colour burst signal. The composite waveform is then fed to a two transistor video amplifier to produce the final output signal.

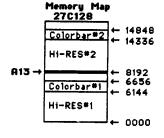

The four graphics screens contained in the E-PROM are designed using a Radio Shack colour computer and then down-loaded into the memory device. The two high-resolution screens occupy approximately 6144 bytes of memory each, and the two colour bar patterns 512 bytes each. A memory map for the E-PROM is shown in Fig.2. High res. screen 1 and colour bar 1 are located in the lower 8k of the device, whilst the other two screens are held in the upper 8k. To switch between the lower and upper areas of memory address line A13 is raised high by means of switch SW3, or by the Fig.2 E-PROM Memory Map timer/sequencer section of the circuit dependant on the position of SW4.

To select the colour bar patterns the CD4066 analog switch IC is switched by the settings of SW1 and SW2, and used to disconnect the E-PROM address lines All and Al2 from VDG control, connecting them to logic high. The VDG is also switched to the graphics mode.

The VDG device is only designed to produce a black and white picture in the high-resolution mode. To overcome this a 555 Timer IC is used to generate the correct timing pulses for the MC1327P to allow a colour signal to be generated. While producing a colour video output this method does have two anomalies. Firstly, if the output is viewed on an oscilloscope it can be seen that the colour burst extends throughout the horizontal sync pulse. However, this has no effect on the video quality. The second problem is due to the fact that the VDG may start on either the rising or the falling edge of the clock pulse, thus there is a chance of getting reversed colours on the high res screens (ie: blues will be red and vice-versa). To correct this simply turn off the power supply and turn on again, repeating if necessary until the correct colours are observed. These problems only occur with the high resolution screens, correct colours are always generated in the low resolution mode used for the colour bars.

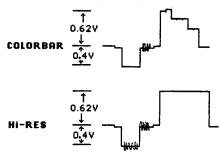

The video output waveforms of the board are shown in Fig.3. The 'white' level generated by the VDG is actually a light shade of grey, thus a ratio of 0.40 volts of sync pulse to 0.62 volts of video should be measured as shown.

The sequencer/timer function is controlled by a 2240 Timer IC. This chip is used to generate two timed outputs to control the selection of VDG the high res/colour bar mode, and the switching of the E-PROM memory banks.

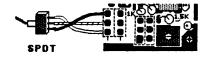

The timing of the display and its sequences are selected by the four switches SW1 to SW4. Table-1 gives the various permutations of the switches and the displays obtained. The board as supplied has links fitted at SW1 and SW4 to provide automatic sequencing through all four screens. These links must be removed before installing the switches. The switches should be wired as shown in Fig.4 so that the centre pin of the switch is connected to the centre pad of the switch PCB location. Position each switch so that when in the up position the top two pads on the PCB for that switch location are connected together, this is the ON position as referred to in table-1.

Switches SW1 and SW4 control the timer functions, SW2 and SW3 control the manual selection of the screens when SW1 and SW4 are both in the off position.

Fig.4 Switch Wiring

#### Fig.3 Video Output Waveforms

| SW1 | SW2 | SW3 | SW4 | SCREENS SELECTED                               |

|-----|-----|-----|-----|------------------------------------------------|

| ON  | x   | x   | x   | Sequences through all four screens.            |

| OFF | ON  | х   | ON  | Sequences through the two high-res screens.    |

| OFF | OFF | х   | ON  | Sequences through the two colour bar screens.  |

| ON  | х   | ON  | OFF | Sequences through high-res 2 and colour bar 2. |

| ON  | х   | OFF | OFF | Sequences through high-res 1 and colour bar 1. |

| OFF | ON  | ON  | OFF | Manually selects high-res screen 2.            |

| OFF | ON  | OFF | OFF | Manually selects high-res screen 1.            |

| OFF | OFF | ON  | OFF | Manually selects colour bar screen 2.          |

| OFF | OFF | OFF | OFF | Manually selects colour bar screen 1.          |

X = Position does not matter.

#### Table 1. Screen select combinations.

NOTE: For repeater applications where computer control of the graphics screens selection is desired links should be fitted between the bottom two pads of SW1 and SW4. Apply a TTL level signal (+5v) from the repeater control circuit to the centre pads of SW2 and SW3 to control the screen selection.

#### SETTING UP

The locations of the various connection points and potentiometers is shown on the PCB overlay in Fig.5. At the time this handbook was published the unit was only available from Bill Brown WB8ELK (address at end of article) as a pre-assembled unit. All that is required to be done is to wire up unit, the switches and other remote controls and the inputs and outputs. A suitable enclosure is the TEN-TEC JW-5. The video input and output connectors should ideally be the BNC variety. The power supply for the unit should be connected via 1nF feed-through capacitors to reduce RF interference.

Connect a monitor or oscilloscope to the output and switch the unit on. Set the VIDEO GAIN potentiometer to the 10 o'clock position and adjust the SYNC LEVEL potentiometer until a video output is present. Set up the switch positions as per table-1 to output one of the colour bar patterns. Re-adjust the SYNC LEVEL potentiometer until the yellow colour bar begins to 'white out'. The SYNC LEVEL control should be backed off until the point is reached where the yellow bar restores to normal colour. The VIDEO GAIN control is now adjusted to give the desired output level. This level may need optimising to give a correct balance between the generated screens and any through video being connected to the VIDEO INPUT, this being passed to the transmitter when the ID board is powered-down. Please note that adjustment of the VIDEO GAIN control beyond the halfway position may result in sync compression.

If external control of the timing circuit is required remove the 500k TIMER ADJUST potentiometer from the printed circuit board and install a chassis mounted type on the front panel. If longer delay times than one minute are required this potentiometer may be increased in value.

This completes the set-up procedure and the unit may now be connected into your ATV transmit system. The screens available are only limited by your imagination and Bill's (or your) computing talents.

Fig.5 Component Layout

23

#### ADDITIONAL INFORMATION

If you are using a quick release E-PROM socket remember to turn off the power before changing the memory device. (This also applies even if you are using a standard socket). Ensure that the locator spot on the E-PROM is aligned correctly with the one on the socket. The E-PROM is a static-sensitive device, and as such should be stored on static-resistant foam or in a plastic storage tube when not in circuit.

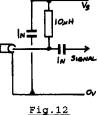

For those who wish to experiment with the colour-burst circuitry the 5.6k resistor adjacent to the 555 timer can be replaced with a 10k potentiometer. This will allow the number of cycles of burst in the high-resolution mode to be varied. Also, the 10-ohm resistor adjacent to the MC1372P IC can be replaced with a 1k potentiometer in order to vary the amplitude of the burst signal. The locations of both resistor changes are shown on the inset in Fig.5.

Horizontal sync pulses can be found on pin-38 of the VDG, and vertical sync on pin-37. The 3.579545MHz clock signal can be found on pin-1 of the MC1327P IC.

For further information, or to order the unit please write to:

Bill Brown WB8ELK, 12536 T.R. 77, Findlay, Ohio 45840, USA. Tel: (419) 422-8206.

For a nominal fee Bill is also happy to layout your graphic screens from your designs and program the E-Proms with the data.

As previously stated, at the time of going to press this unit was only available pre-assembled. However, please check with Bill as to whether he is now able to supply in kit form.

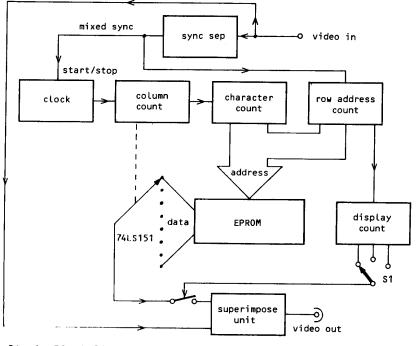

### **TELETEXT PATTERN GENERATOR**

There are plenty of circuits around for generating patterns on a television screen, and similarly there are quite a number devoted to generating alphanumeric and graphics characters. Now though, in the design presented here, both functions are made available at the same time, providing a very versatile system of electronic picture generation for the amateur shack or studio.

Teletext has been around in the U.K. for some years now under the names 'Ceefax' (BBC) and Oracle (IBA). Similar services are also available over much of Europe and many other countries throughout the world. It is not surprising then that a dedicated set of integrated circuits have been made available to satisfy the considerable demand, and it is these devices upon which this design is based. First though let's remind ourselves of the principles of the Teletext medium.

#### TELETEXT

The top few television lines of each television field are not used for carrying picture information as such, but for transmitter control data, specialised waveforms for checking system parameters (group delay, frequency response etc.) and other purposes. Two of the lines are also used to transmit a data system known as Teletext, whereby television sets fitted with the appropriate decoder can read this data and thus the relevant information contained in it, which comprises everything from TV programs, weather, travel, shopping etc.

The decoder contains a 1K RAM chip which can accept a page of information at a time. All the pages are transmitted serially, but only one may be stored in the decoder at a time, once a different page number is selected by the user when it appears at the decoder the data is stored in the RAM chip. The data format is 7-bit words representing numbers from  $\emptyset$  to 127, each of which represents a particular ASCII character, graphic shape, colour or control code. These characters and shapes are decoded from the data stream and presented to the screen to provide the pictures and information which are read off the screen, rather like reading a newspaper. When that page has been read another can be selected and the whole process repeated.

#### THE TELETEXT LSI INTEGRATED CIRCUITS

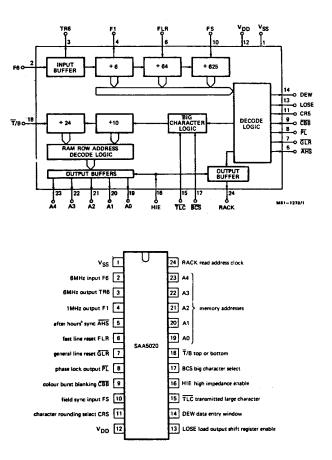

#### SAA5020 TIC (timing chain)

The divider stages in the TIC integrated circuit sub-divide the 6MHz clock signal down to 25Hz, the television frame rate, and generate all the timing signals for the teletext display. Fig.1 shows a simplified block diagram of the SAA5020 circuits and a pin-out of the device. During the display period, a 1MHz clock signal RACK (Read Address Clock) takes over from WACK (Write Address Clock) to step the character addresses. The address counter (74LS393) is cleared at the end of every line and reset to the first position. After every ten lines during the display, the TIC steps the row address on by one to access the next row of characters in the memory.

Τn addition to providing all the timing signals for the display, the TIC also generates a complete composite sync signal which is used to drive the PAL coder and 'stand provide a alone' system free of any external sync requirements. The TIC is capable of genlocking to an external source but this facility has not been implemented here in order to simplify the design. Frame lock could easily be added by the reset input on pin-10 which requires a positive TTL pulse to accomplish locking. This input could be clocked at 60Hz if 525-line operation required, is not forgetting of course to adjust the frequency of the 6MHz clock to correct the line speed. The mixed sync signal is to the European of standard five broad pulses per vertical interval.

#### FIG.1 SAA520 TIC Block Diagram and Pin-Outs

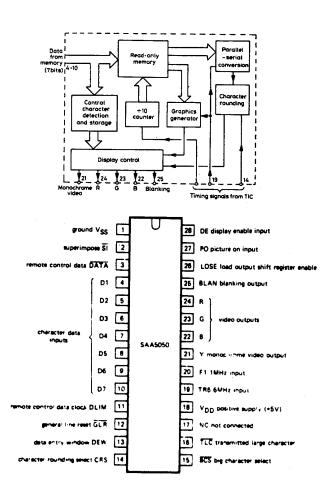

#### SAA5050 TROM (teletext read-only memory)

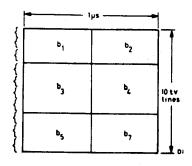

The read-only memory of the TROM IC converts the 7-bit character data from the memory into a dot matrix pattern. This matrix is in a 7-by-5 dot form for each character. The TROM also contains a 'character rounding' facility which effectively increases this matrix to 14-by-10 dots, giving improved definition to the displayed characters. Fig.2 shows a simplified block diagram of the SAA5050 circuits and its pin-outs.

Timing signals are fed to the TROM from the TIC IC. Character video output signals are provided, and these comprise a monochrome-only signal (Y) and RGB signals for a colour encoder. The blanking output (not used in this application at present) enables a through television video signal to be blanked out when a teletext subtitle is to be displayed ('1' gives 'picture blank', '0' gives 'picture on'). The blanking-out takes the form of a 'black box' around the teletext characters.

Although not used at present in this unit it is useful to describe the function of the monochrome tevt signal (Y). It is provided for monochrome displays; that is, it does not include background video information. However, it is also necessary if. in а normal colour display, inlay of characters into the picture television is required; it is then used AS an inlay blanking signal. When text and video are mixed. the readability of the display is greatly improved if the text is inlaid. rather than simply added on to the television video. The readability is further enhanced if the picture contrast is automatically when reduced text and video are mixed.

#### Fig.2 SAA5050 TROM Block Diagram and Pin-Outs

This can be performed by using the 'superimpose' output (pin-2) from the TROM IC.

The TROM generates 96 alpha-numeric and 64 graphics characters; the alpha-numeric character set is shown in Fig.3. In addition there are 96 special characters for controlling the display. Input to the device is a 7-bit code from the E-PROM, each character code defining a dot matrix pattern. The character period is 1uS and the character dot rate is the same as the master clock. The video output signals are all open-collector TTL signals and are at the correct amplitude for feeding the colour encoder shown elsewhere in this handbook.

|                      | ·              | 1 <b>11</b>                                                                                                      | · ···································· |   |

|----------------------|----------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------|---|

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                | 5/9 6/1                                                                                                          |                                        | 2 |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      | 4/10 6/2       | 5/10 5/2                                                                                                         | A                                      | 1 |

|                      |                |                                                                                                                  |                                        |   |

| <br>±d bititi bititi | ┫ ┣╋╋╋╋┥ ┝╋╋╋╇ |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        | 1 |

|                      |                |                                                                                                                  |                                        |   |

| 3/12 4/4             |                | A                                                                                                                |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                | 5/12 6/4                                                                                                         |                                        |   |

|                      |                | 5/12 6/4<br>6-112 6/4<br>6-112 6/4<br>6-112 6/4<br>6-112 6/4<br>6-112 6/4<br>6-112 6/4<br>6-112 6/4<br>6-112 6/4 |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

|                      |                |                                                                                                                  |                                        |   |

Fig.3 SAA5050 Alpha-Numeric Character Set

#### CIRCUIT DESCRIPTION

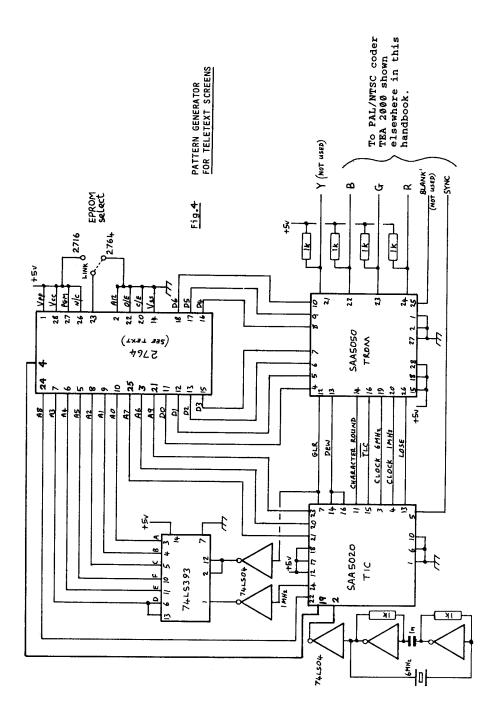

The circuit diagram is shown in Fig.4. The 6MHz system clock is generated by two gates of a 74LSØ4 Hex Inverter and is controlled by a 6MHz crystal. This clock is used to derive all the necessary timing edges for all the waveforms. The 24-pin SAA5020 Timing Chain IC generates the mixed sync, colour burst and, with the aid of the 74LS393 Counter, all the memory addresses for reading the E-Prom. This IC is capable of genlocking so that the video display is synchronous with an external source, but this has not been implemented here in order to simplify the circuit. Frame lock could easily be added by the reset input on pin-10 of device, which requires a positive TTL pulse to accomplish this task. This input could also be clocked at 60Hz for 525-line working as well as adjusting the frequency of the 6MHz clock to correct the line speed. The mixed sync is to the European standard of five broad pulses per vertical interval.

I

The SAA5050 Teletext Character Generator IC is a 28-pin device which incorporates a fast access character generator ROM (4.3K) and the decoding circuitry for all the teletext control characters. The device generates 96 alpha-numeric and 64 graphic characters. In addition there are 96 special characters for controlling the display. The input to the device is a 7-bit code from the E-Prom, each character code defining a dot matrix pattern. The character period is luS and the character dot rate is the same as the master clock. The video outputs from the device comprise a monochrome ie:6MHz. output (Y output, not used here), and Red, Green and Blue. These outputs are all open collector TTL signals and are at the correct level for feeding, along with the mixed sync, the colour coder shown elsewhere in this handbook.

The RAM memory used in television teletext decoders has been replaced here by the E-Prom, which may be either a 2716 or 2764 type. If a 2716 is used it should be located at the bottom of the socket leaving the top four pins (two each side) vacant, and the link at pin-23 changed to the +5v position. A pre-programmed E-Prom can be obtained from BATC Members Services with the pattern shown in Fig.3. Alternatively, for those able to program their own devices Fig.4 shows the area of the memory which is addressed by the circuit. For those owning Spectrum computers an E-Prom Blower is described elsewhere in this book.

#### CHARACTER MAPPING AND FORMAT

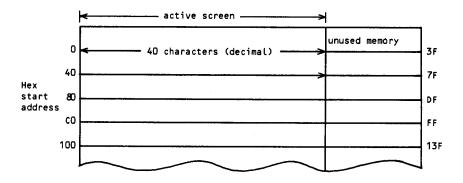

The screen memory map is peculiar to this circuit. The format is 40 characters across the screen stored in 64 bytes of memory, the remaining 24 bytes being skipped over and the next line of information starting at memory location 65 (see Fig.5).

#### Fig.5 Screen Memory Map

Each character occupies a space six dots wide by ten lines high, (Fig.6) one dot space is left between adjacent characters and one television line space left between rows. Alpha-numeric characters are generated on a 5x9 matrix thus allowing space for true descenders. Each of the 64 graphic characters is decoded to form a 2x3 block arrangement which occupies the complete 6x10 dot matrix. The alpha-numeric characters are rounded, that is a half dot is inserted before or after a whole dot in the presence of a diagonal in a character matrix. Graphic characters mav be either contiguous or separated (Fig.7). The control characters allow the nature of the display to be changed, eg: double height, character colour, flashing display, background colour etc.

table in Fig.8 shows the complete The character and control code set and gives the HEX code for each. The selection between alpha-numeric or graphic character for each HEX code is carried out by first selecting or cancelling the graphic mode, using the appropriate code for that instruction.

Fig.6 Character Cell

This is exactly the same method as is used in home computers.

alphanumerics & graphics 'space' char. 0000010

alphanumerics char. 1011010

alphanumerics or blast-through alphanumerics char. 0001001

alphanumerics char. 1111111

contiguous graphics char. 0110111

separated graphics char. 0110111

separated graphics char. 1111111

Display colour

contiguous graphics char. 1111111

|                          | 2ND HEX DIGIT (DOWN) > IST. HEX DIGIT (ACROSS) |                              |    |   |         |  |    |                    |   |  |   |  |

|--------------------------|------------------------------------------------|------------------------------|----|---|---------|--|----|--------------------|---|--|---|--|

| <b>↓</b>                 | 0                                              | 1                            | 2  | 2 | 3 4     |  | 4  | 5                  | 6 |  | 7 |  |

| 0                        | NUL.                                           | <u>DLE</u> #                 |    |   | 0       |  | 0  | P                  | Ð |  | Ð |  |

| 1                        | Alpha <sup>n</sup><br>Red                      | Graphics<br>Red              |    |   | 1       |  | A  | Q                  | a |  | ٩ |  |

| 2                        | Alpha <sup>n</sup><br>Green                    | Graphics<br>Green            |    |   | 2       |  | B  | R                  | Ь |  | • |  |

| 3                        | Alpha <sup>n</sup><br>Yellow                   | Graphics<br>Yellow           | £  |   | 3       |  | С  | S                  | C |  | S |  |

| ٤                        | Alpha <sup>n</sup><br>Blue                     | Graphics<br>Blue             | \$ |   | 4       |  | D  | T                  | ٩ |  | t |  |

| 5                        | Aipha <sup>n</sup><br>Magenta                  | Graphics<br>Magenta          | %  |   | 5       |  | E  | U                  | e |  | U |  |

| 6                        | Alpha <sup>n</sup><br>Cyan                     | Graphics<br>C yan            | &  |   | 6       |  | F  | $\bigtriangledown$ | ſ |  | V |  |

| 7                        | ₹₹<br>Alpha <sup>n</sup><br>White              | Graphics<br>White            |    |   | 7       |  | G  | ₪                  | g |  | E |  |

| 8                        | Flash                                          | Conceal<br>Display           |    |   | 8       |  | H  | X                  | h |  | × |  |

| 9                        | ±≢.<br>Steady                                  | ##<br>Contiguous<br>Graphics |    |   | 9       |  | [] | $\mathbf{Y}$       | • |  | y |  |

| A                        | ##<br>End Box                                  | Separated<br>Graphics        | ×  |   |         |  | ט  | Z                  |   |  | Z |  |

| в                        | Start Box                                      | <u>esc</u>                   | Ð  |   | $\odot$ |  | K  | Ð                  | k |  | ٦ |  |

| с                        | ¶∄<br>Normal<br>Height                         | ##<br>Black<br>Background    |    |   | 2       |  |    | 2                  | 1 |  |   |  |

| Ð                        | Double<br>Height                               | New<br>Background            | 0  |   | =       |  | M  | Ð                  | 6 |  | ٩ |  |

| E                        | <u>so</u> *                                    | Hold<br>Graphics             |    |   | Ð       |  | Z  | •                  | n |  | ÷ |  |

| F                        | <u>\$1</u> *                                   | 常語<br>Release<br>Graphics    | Ø  |   | ?       |  | 0  | Ħ                  | 0 |  |   |  |

| EG: HEX CODE FOR A' = 41 |                                                |                              |    |   |         |  |    |                    |   |  |   |  |

Fig.8 Hex Codes for Character Set

#### CONSTRUCTION

A pre-drilled printed circuit board for this unit is available from BATC Members' Services. The PCB will accomodate either HC6U or miniature crystal packages. It is recommended that all the IC's are mounted in sockets, and as the circuit board is single-sided this will not cause any problems. The E-Prom can be a 2716, 2732 or a 2764 type. Pin-23 is left floating on the PCB, thus a solder bridge is all that is required to suit the appropriate device. The 2716 and 2732 types are housed in 24 pin packages and should be fitted into the socket so that the unused holes (socket locations 1, 2, 27 & 28) are at the top.

As previously stated, the RGB and sync outputs are at TTL, and suitable for feeding directly into the PAL/NTSC coder shown elsewhere in this handbook.

A selection of pre-programmed E-PROM's is available from Members's Services, but only with the patterns shown customised with your own call sign, QTH etc.

The chip set which decodes the data and display can often be found on the surplus market at very reasonable prices. Alternatively, they are regularly advertised in the national magazines by the large electronic spares retailers.

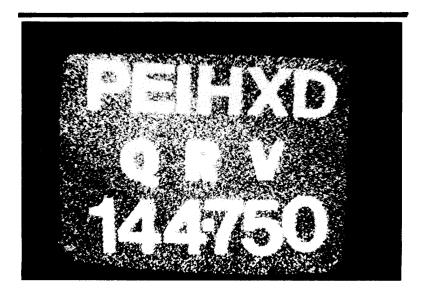

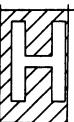

An example of a screen produced by the Teletext pattern generator.

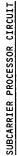

### DUAL-STANDARD COLOUR CODER

Several of the projects in this handbook require the addition of a colour coder to provide a suitable video output waveform for use in the shack. Although this simple coder could be added on to the PCB's for each unit, it has been designed as an add on to allow it to be used with other units not described in this book. The coder is suitable for both PAL and NTSC standards and is easily configured for either.

#### CIRCUIT DESCRIPTION

The colour coder is contained within a single chip the TEA2000. This device is capable of encoding to NTSC or PAL standards by either grounding pin-14 for NTSC, or leaving it 'floating' for PAL. The crystal connected to pin-13 (x2) needs to be twice the frequency of the colour subcarrier, ie:8.867MHz for PAL and 7.1276MHz for NTSC. L1 should be adjusted for maximum subcarrier and the burst position may need altering between standards, this is done by changing the value of R1. The delay line at pin-8 should be a 270nS type (Philips V8470 270nS/900-ohm), as found in domestic TV sets.

#### CONSTRUCTION AND SET-UP

A printed circuit board is available from Members' Services for this project. The TEA2000 and the delay line may also be available, please check your latest copy of CQ-TV.

Once all the components have been fitted and soldered to the pcb connect the input signals, the DC supply and a colour monitor to the output. Set the solder link at pin-14 of the TEA2000 to either floating for PAL, or to ground for NTSC (also check that the correct frequency crystal is fitted for the standard in use as given above). Adjust VC1 until colour-lock is obtained, confirming that the trimmer is in the centre of the lock-in range. Adjust L1 for maximum colour saturation.

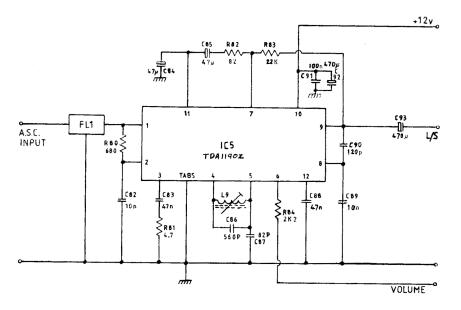

### VIDEO DISTRIBUTION AMPLIFIER

A problem often encountered in the shack is the need to supply several different pieces of equipment from the same video source. What's required is a simple, but effective, video distribution amplifier. The unit described here fulfils that requirement, in fact it is so simple it almost belies description. It will provide three outputs from one input.

#### CIRCUIT DESCRIPTION

The heart of the unit is the video switching IC the TEA5114. In this circuit this chip is not used for its switching capabilities, but for its signal amplification and isolation properties. The input video signal is fed to each of the normally closed inputs of the device via separate decoupling capacitors. The three outputs are taken via 15-ohm resistors, maintaining the impedance at 75-ohms.

The switching control inputs of the TEA5114 (pins-10, 12 & 15) are all grounded, thus preventing operation of the switches. However, if it is required to be able to switch off the various outputs, then by applying a MAXIMUM of  $\pm 2.5$  volts to the appropriate control input, the respective output will be switched off.

#### <u>CONSTRUCTION</u>

This unit being so simple can be constructed in a very short time using Vero-board, thus a printed circuit board has not been made available. No special attention needs to be paid to the layout of the few components. A single 12 volt power rail is required capable of providing 150mA.

Video Distribution Amplifier

# **A DIGITAL FRAMESTORE**

This project is fairly complex and ideally should not be attempted by the inexperienced constructor

The television signal that is handled by most of our television equipment consists of an analogue part (the picture content) and a digital part (the timing or sync. pulses). The analogue part has continuous variations of amplitude and is easily affected by distortion or interference.

In transmitting signals Frequency Modulation is capable of higher quality, once a threshold is reached. The amplitude of the received signal does not matter and most interference etc is, essentially, sliced off by the processing of the signal in the receiver. In a similar way digital audio, from tape or compact disc, is capable of high quality if suitably processed. If, therefore, the analogue part of a video signal can be turned to a digital signal we can process it in various ways, without causing distortion. In video, in fact, it is the ability to process the signal which is the greatest benefit.

In order to make use of digital video signals, a number of decisions need to be made as to how the video is to be processed. For example, the video may be digitised in composite or component form, the signal may be sampled at various rates, and so on. In this project many of these options are left open, in order to make it adaptable to future expansion or different television standards. For colour working, however, the picture signals will be treated in component form - which will enable standards conversion, for example, if that is later required. The project is designed in a modular form, for ease of testing and to allow for improvements to a section without making the remainder redundant.

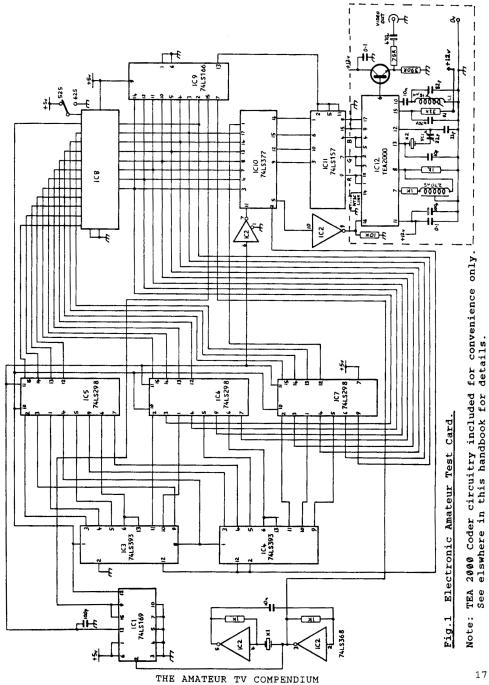

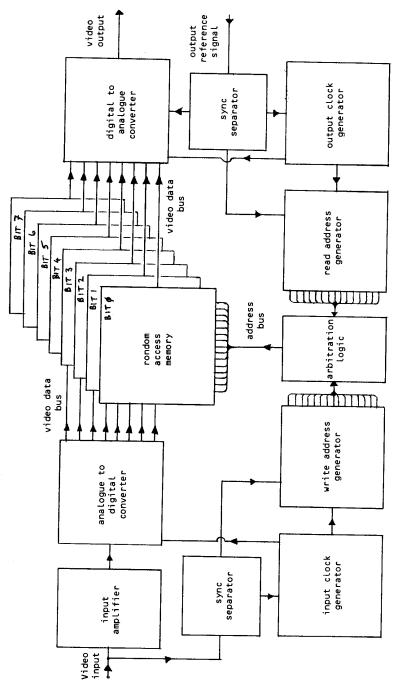

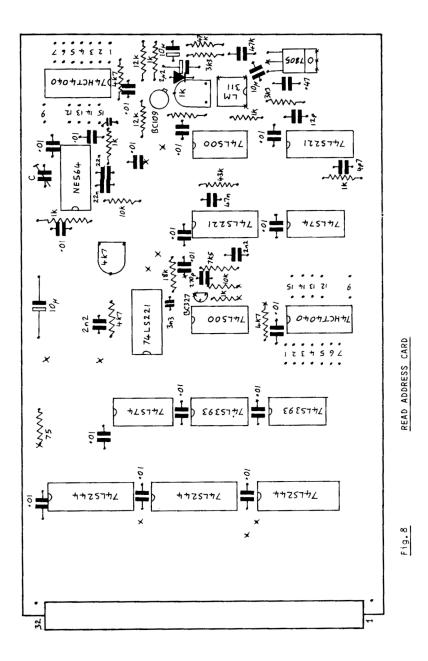

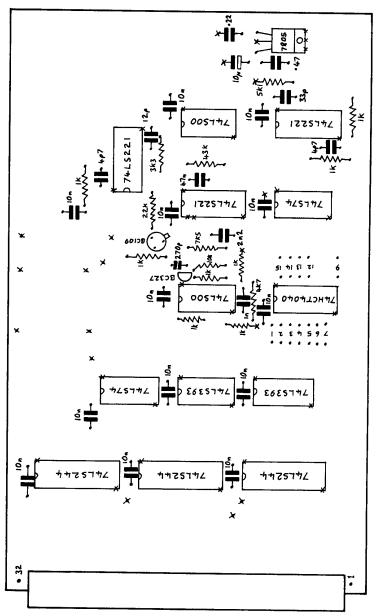

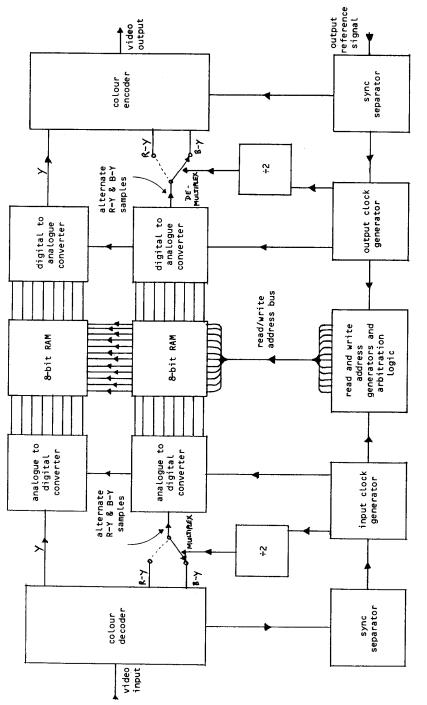

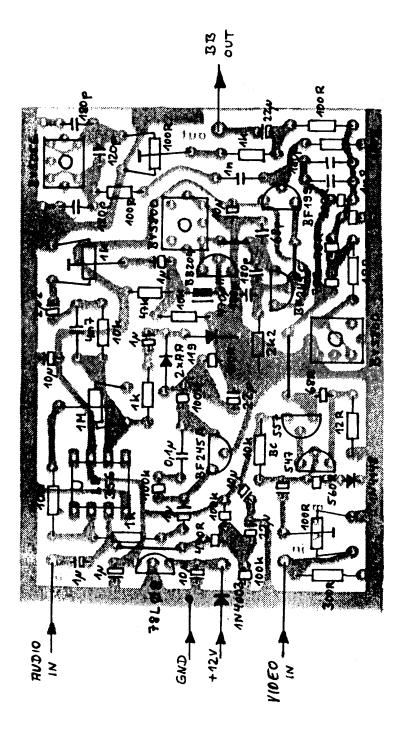

The essentials of a digital video system are shown in the block diagram (Fig 1). The video input has first to be sampled at an appropriate rate. Thus a clock pulse locked to the incoming signal will be needed for this. The resultant digital video is then processed, which may include storing in memory. For this an address will need to be determined for each point of the picture to be written into the RAM. To read out the signal a series of read addresses will need to be sent to the memory, and the signal may be further processed. The outgoing digital signal will then need to be converted back into a conventional video signal, which will need a clock pulse locked to the read addresses. These various circuits are accomodated on a series of Eurocard printed circuit boards available from Member's Services, which can be added to as the system develops.

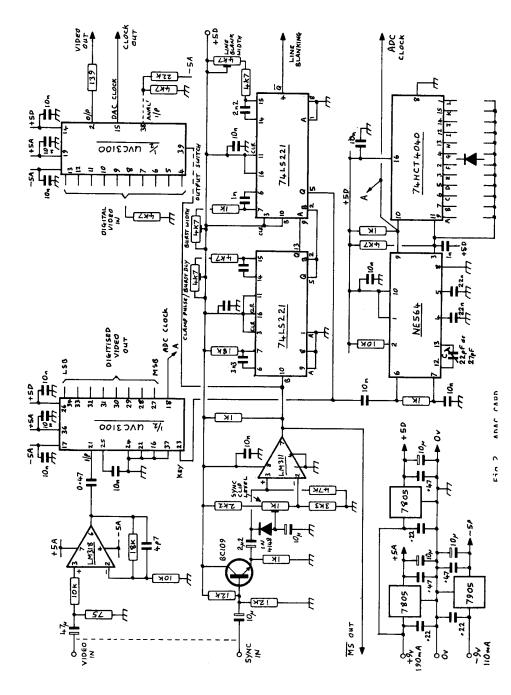

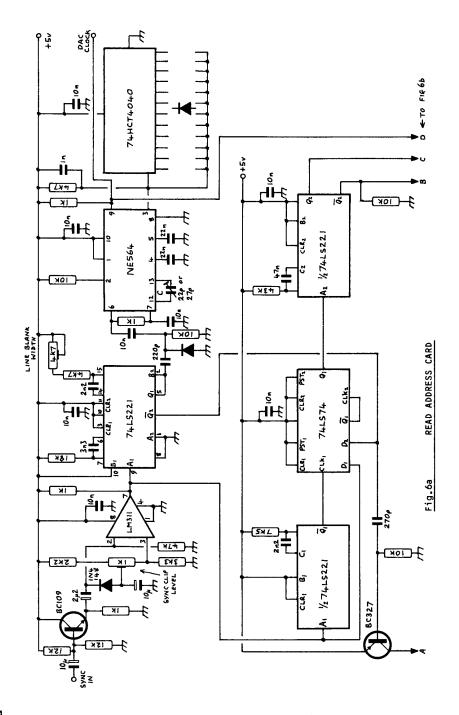

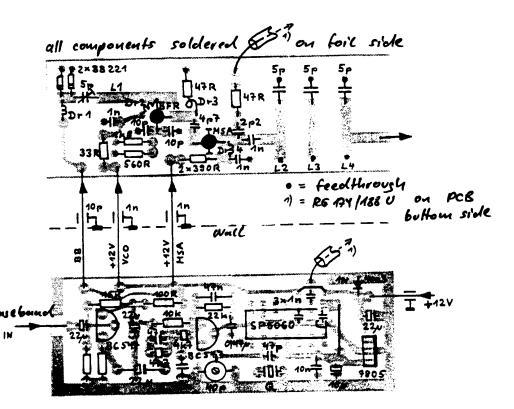

#### ANALOGUE TO DIGITAL TO ANALOGUE CONVERTER

This first board contains the circuits to carry out the conversion from analogue video to digital signals, generate the incoming locked clock pulses, and convert the digital signals back to an analogue video signal. The circuit is shown in Fig 2 and works as follows: The incoming video signal is terminated by the 75 ohm resistor, then amplified by the LM318. This has a capacitor across the feedback resistor (4p7 in the diagram) to provide some high frequency roll-off to the response, and reduce the patterning that can result from beats

Fig.1 FRAME STORE BLOCK DIAGRAM

THE AMATEUR TV COMPENDIUM

38

THE AMATEUR TV COMPENDIUM

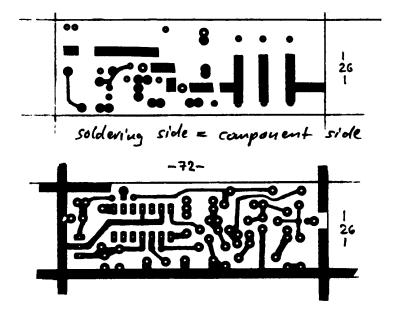

Fig.3 A-D/D-A PC BOARD LAYOUT

39

between the clock pulses and high frequencies in the video signal. Increasing this capacitor will reduce the video bandwidth of this amplifier, and vice versa. The video is then fed to the UVC3100, which clamps the video signal to black level, and then carries out an A-D conversion. The video is sliced into 256 possible grey levels, and coded into an 8 bit binary word, for each sampling point.

A sync signal is either taken from the incoming video or as a separate feed, buffered by the BC109, and fed to the LM311 comparator circuit which slices the sync pulses off. The output is therefore inverted These are fed to a 74LS221 monostable, which mixed sync pulses. removes the half line pulses, and triggers two further monostables one producing a pulse that lasts until the end of line blanking (required by the write address circuit) the other producing a delay to trigger the fourth monostable to generate a clamp pulse for the UVC3100 input clamp. This can conveniently be set to coincide with the colour burst. This signal also triggers the phase comparator of the phase lock loop that generates the incoming video clock pulses, which is made by the NE564 and 74HCT4040. It can be adapted to run at almost any desired clock rate by choosing a suitable value for the capacitor C at NE564 pins 12 and 13 and by changing the programming diodes of the 74HCT4040.

The clock pulse is not locked to the subcarrier frequency, so that if the picture is to be rescaled, or in some other way distorted spacially, the colour can still be handled. This will require the colour to be handled in component, not composite form.

Also on this board, because it is contained in the UVC3100 I.C., is the D-A converter. This takes in a 10bit digital signal - of which the 8 most significant bits can be used at this point (pins 4 - 11 in order) - and converts it. There is also an analogue switch at the output which can be used to insert clean sync pulses etc. The card will also accept on board voltage regulators, which together with decoupling at the supply pin of each I.C. will prevent noise problems.

This board can be made tested and used on its own and the layout is shown in Fig 3. The 7805 regulators use the ground plane directly as the heatsink, whilst the 7905 must be insulated from the copper bracket which transfers its heat to the ground plane.

The oscillator frequency is now decided. For those who wish to decide this themselves, the method is given below - others can move on to the next paragraph! The UVC3100 can handle a sampling frequency up to about 30MHz, but a much lower frequency is quite acceptable for video. If the data is to be stored in memory then this may decide the maximum. For example, a 256k RAM has 262144 locations. The active part of a 625 line picture is contained in 288 lines per field, so if the memory were filled up then there would be 910 (262144 / 288) samples per line. These occupy the active part of a television line (52 micro seconds at 625 lines) so across the full line (64 micro seconds at 625 lines) there are 1120 samples (910 x 64 / 52). Each sample takes 64 / 1120 micro seconds - which is 57.14 nS, corresponding to a frequency of exactly 17.5MHz. To set the NE564 frequency, we need a capacitor C where:

C = 400 / f ('C' is measured in pF, 'f' clock frequency in MHz). This comes out at 22.8pF in the example so a 22pF trimmer capacitor is fitted. Diodes are inserted in the positions that, from Table-1, add up to the number of samples per total line (1120) in order to program the 74HCT4040 divider. In the example this is F, G and K (32 + 64 + 1024) - there is only one possible combination for any particular clock rate. By following the method above, any desired clock rate can be accomodated on this board for any television standard.

| DIODE<br>LOCATIONS   | A | В | с | D | E  | F  | G  | Н   | I   | J   | ĸ    | L    |

|----------------------|---|---|---|---|----|----|----|-----|-----|-----|------|------|

| NUMBER OF<br>SAMPLES | 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | 256 | 512 | 1024 | 2Ø48 |

#### TABLE-1

Using diodes at F, G, I and J, (Fig's.3, 8 and 9 locations 2, 4, 12 and 14) together with a 27pF trimmer capacitor gives a 13.5MHz clock rate, whilst diodes at F, G and K (Fig's.3, 8 and 9 locations 2, 14 and 15) with a 22pF trimmer capacitor give a 17.5MHz clock (both for 625 line / 50 field pictures).

#### SETTING UP THE ANALOGUE BOARD

Now apply a 1 volt p-p video signal to the input. Monitor the signals at the LM311 pins 2 and 3 with a D.C coupled oscilloscope, and adjust the slice preset potentiometer, so that the slicing point is about half the sync pulse amplitude. The oscilloscope is now used to adjust the three other presets - putting the incoming video on one channel and setting the end of blanking to coincide with the start of the incoming video. Also set the clamp pulse to be between the sync pulse and start of active part of line (i.e., where the colour burst would be) this is quite easy.

Trimmer capacitor C at the NE564 is adjusted as follows: Monitor the signal on pin-6 of the NE564 on channel-1 of a twin beam oscilloscope, connect channel-2 to pin-6 of the NE564. Trigger the oscilloscope from channel-1 and adjust trimmer C until the signal on channel-2 is locked to channel-1

Lastly, switch off, couple the digital output lines in order to the eight most significant digital input lines, and connect the two clock lines together. Apply the video signal to the board input, and a reconstructed copy should be seen at the DAC output. Looking at it on the oscilloscope, it will appear to be displaced about 150 - 200nS to the right (i.e. 3 clock pulses), the time taken for all the processing.

This circuitry has been designed and tested using the UVC3100 analogue-to-digital interface circuit. It is one of several similar circuits which may be used with minor circuit changes. The UVC3101 is pin for pin matched to the '3100 device, but has a slightly less linear D-A converter. The UVC3120 lacks the input clamp, buffer and voltage reference circuitry. Pin-25 must be held at +2V, and pins-20, 22 and 23 grounded if this circuit is used. The UVC3130 is virtually the same as the '3100, but requires +5V analogue supply to pins-1 and 40 (which are unused pins in the other versions).

As it stands the board can be used to change the number of grey levels

THE AMATEUR TV COMPENDIUM

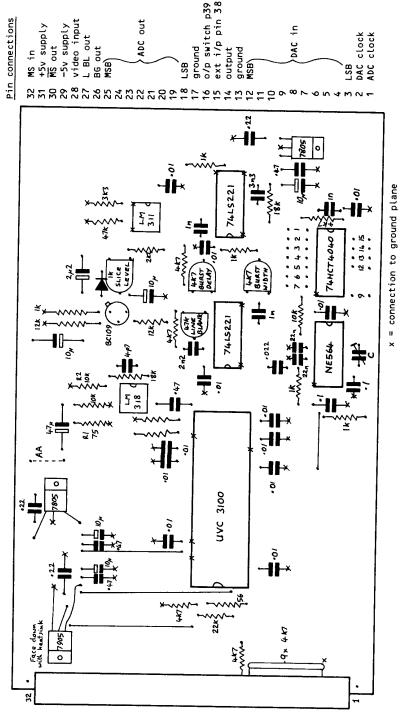

Pin Connections

43

Fig.5

in the picture. By putting switches in the digital path, or by inverting the digital signals, negative images can be selected. However, if the digital data is stored in memory a much wider range of applications become possible.

- NOTES: 1) If the input is not required to be terminated in 75-ohms, remove the 75-ohm resistor connected to ground at the junction of the 47uF input capacitor and the 10k resistor.

- Replace the 10k resistor to ground connected to pin-2 of the LM318 with a 22k for composite colour signals.

- Insert link A-A to enable sync extraction from the incoming signal.

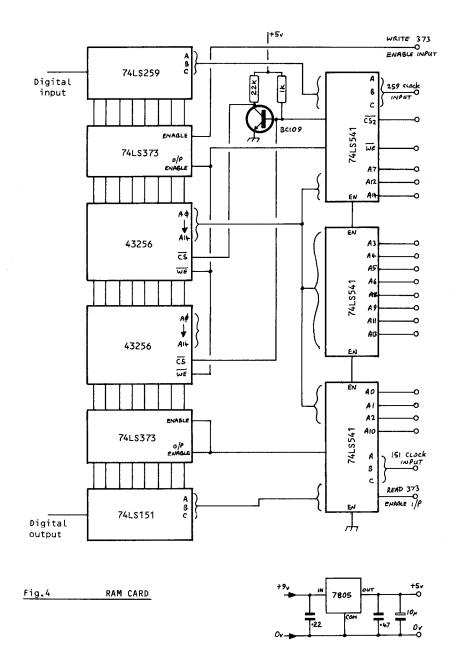

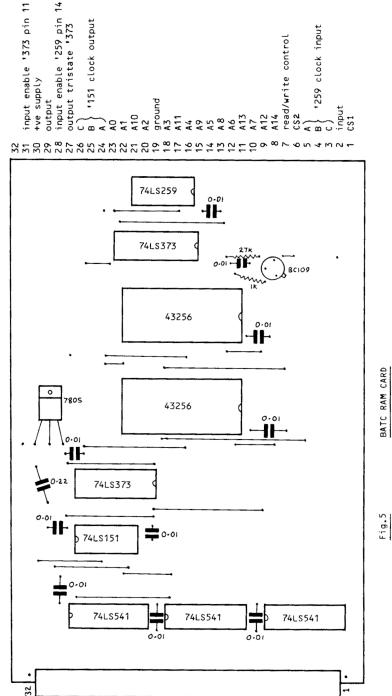

#### RAM AND READ/WRITE ADDRESS CARDS

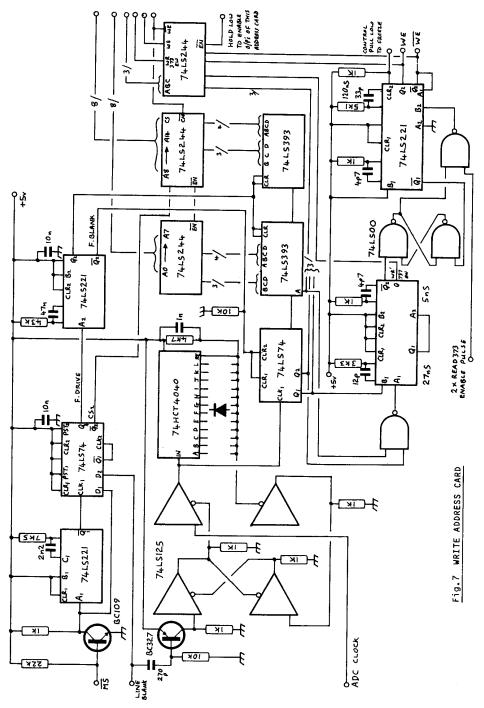

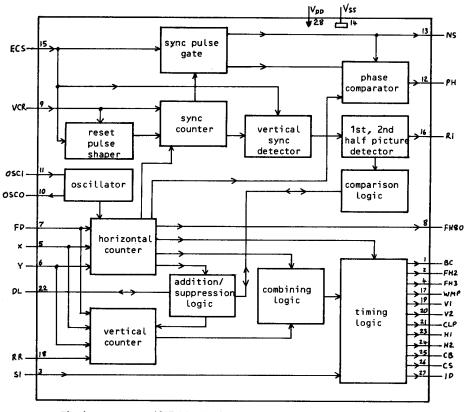

To put the data into RAM is not quite staightforward. Even at the 'slow' speed of 13.5MHz, a new sample comes along every 74nS or so at 17.5MHz this happens every 57nS. The data has to be read into the memory and also a (probably different) sample read out sufficiently quickly to allow the next sample to be read in. At first this may appear to be impossible, or to at least need RAM with an access time of less than 28nS. The trick is to allow the A-D converter to send data every 74nS, but only ask the memory to accept data every 592nS. Using readily available 120nS access time RAM devices there is now plenty of time to do this, and read out a sample every 592nS as well. It would appear that seven out of eight samples will be lost as a result, but they are stored temporarily, and eight parallel bits of data read to the main RAM every 592nS. In many designs the temporary storage is done in shift registers, but here (Fig 4) the addressable latch (74LS259) does the task. Once the 8 latches are full, the data is held in latches (74LS373) until the RAM is ready to accept it. In a similar way, the data is read out of the RAM as eight parallel bits of data, held temporarily in a latch (74LS373 again) and returned as a serial stream of digital video by the data selector (74LS151). Static RAM is used, as this greatly simplifies the addressing requirements, which will be an advantage if extra facilities are added later. A 32k x 8 device will conveniently store a field of one bit of data, so the PCB's accept two of these to store one frame. Each single RAM card (Fig 5) can be tested separately and the memory

expanded bit by bit (Pun intended !) as circumstances allow. A commercial system would no doubt have all the memory on a single high density board, but in this way it can be built by the average constructor, without too much worry about exceedingly fine tracks. For testing, RAM modules can be readily interchanged.

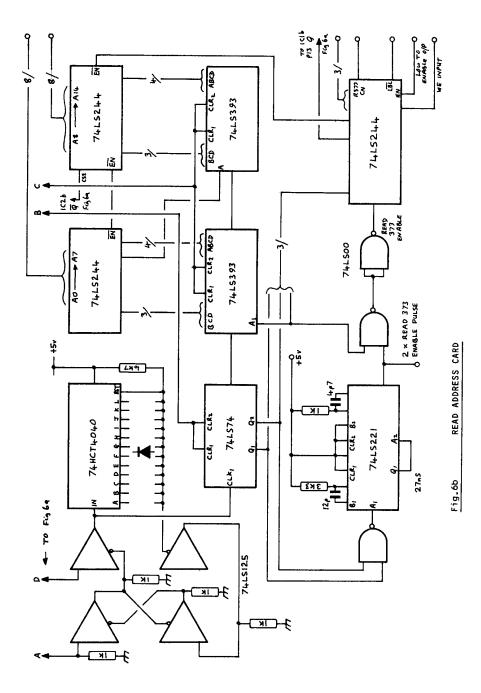

In order to use the memory two more modules are needed. These generate the read addresses (Fig 6) and the write addresses, plus arbitration logic (Fig 7) respectively. The arbitration logic is needed to interleave the read and write operations so that the system does not attempt to read and write at the same instant. By having separate read and write addresses the outgoing picture can be differently timed to the ingoing one, which is one of the main uses of a framestore. By stopping any further write signals, of course the memory will continue to read the existing data - i.e: a freeze frame.

The read address card has first to generate line blanking and a clock

THE AMATEUR TV COMPENDIUM

47

pulse locked to the sync pulses timed to suit the outgoing video signal. This is done in a very similar way to the incoming video clock pulses generated on the A-D / D-A card. The comparator inputs are reversed so its output is now non-inverted sync pulses. The positioning of the diodes and choice of NE564 oscillator capacitor are as described above.

Both address cards must count the appropriate number of clock pulses for the active part of each line (910 in the example worked through above). These must begin at the end of the line blanking period. The line blanking signal sets an R-S bistable, which allows clock pulses to a 74HCT4040 counter. This is programmed to divide by the number of pixels in the active line (910) and its output resets the R-S bistable, inhibiting the clock pulses until the next end of line blanking. The clock pulses also go to a counter chain made up of an 74LS74 and two 74LS393's, which generate the address codes for the memory boards. These counters are reset to zero by the frame blanking signal (inverted for the 74LS74). The address codes are buffered by the 74LS244's before joining a common address bus.

| READ | ADRRESS CARD             | WRITE ADDRESS CARD |                   |  |

|------|--------------------------|--------------------|-------------------|--|

| PIN  | CONNECTION               | PIN                | CONNECTION        |  |

| 1    | +ve Supply               | 1                  | +ve supply        |  |

| 2    | 373 Enable pulse o/p     | 2                  | Freeze control    |  |

| 3    | CS-2                     | 3                  | CS-2              |  |

| 4    | A14                      | 4                  | A14               |  |

| 5    | A10                      | 5                  | A10               |  |

| 6    | A13                      | 6                  | A13               |  |

| 7    | A9                       | 7                  | λ9                |  |

| 8    | A12                      | 8                  | A12               |  |

| 9    | A8                       | 9                  | A8                |  |

| 10   | A11                      | 10                 | A11               |  |

| 11   | Ground                   | 11                 | Ground            |  |

| 12   | Ground                   | 12                 | Ground            |  |

| 13   | A7                       | 13                 | λ7                |  |

| 14   | A6                       | 14                 | <b>A</b> 6        |  |

| 15   | A2                       | 15                 | λ2                |  |

| 16   | A5                       | 16                 | A5                |  |

| 17   | A1                       | 17                 | A1                |  |

| 18   | A4                       | 18                 | λ4                |  |

| 19   | AØ                       | 19                 | AØ                |  |

| 20   | A3                       | 20                 | A3                |  |

| 21   | Enable 244 O/P's         | 21                 | Enable '244 O/P's |  |

| 22   | A 151 Clock I/P          | 22                 | A 259 Clock O/P   |  |

| 23   | WE Input                 | 23                 | WE Output         |  |

| 24   | B 151 Clock I/P          | 24                 | B 259 Clock O/P   |  |

| 25   | C 151 Clock I/P          | 25                 | C 259 Clock O/P   |  |

| 26   | Line Blank Out           | 26                 | WE Output         |  |

| 27   | MS                       | 27                 | 373 Enable Input  |  |

| 28   | Read 373 Enable          | 28                 | Write 373 Enable  |  |

| 29   | 244 Enable (Card Select) | 29                 | 244 Enable(C/S't) |  |

| 30   | Spare                    | 30                 | Line Blank I/P    |  |

| 31   | DAC Clock Output         | 31                 | ADC Clock Input   |  |

| 32   | Video/Sync Input         | 32                 | MS                |  |

#### TABLE.2 EDGE CONNECTOR DETAILS FOR READ AND WRITE ADDRESS CARDS

49