# THICRO AND TELEVISION PROJECTS

BY TREVOR BROWN

## **BRITISH AMATEUR TELEVISION CLUB**

## **ACKNOWLEDGEMENTS**

### The Engineers

Trevor Brown G8CJS Clifford Brownbridge G6BIN Richard Russell G4BAU Jacques Pochet F6BQP John Lawrence GW3JGA David E Jones GW8PBX

### The Draughtsmen

John Wood G3YQC Tony Marsden G6JAT

### The Writers

Andrew Emmerson G8PTH Dave Halliday Peter Delaney G8KZG Peter Ward G4GYI

### Prototypes

Chris Lewis G6ACL

### Software

Robin Stephens G8XEU

## **CONTENTS**

### CHAPTER 1

Simple ATV Station

Test Pattern and Sync Generator

Electronic Caption Writer

Simple Vision Switcher

### CHAPTER 2

Best of the Handbooks

Electronic Test Card

PAL Coder

### CHAPTER 3

Secam Coder

### CHAPTER 4

Home Computers

Spectrum User Port

Computer Controlling Character Generators

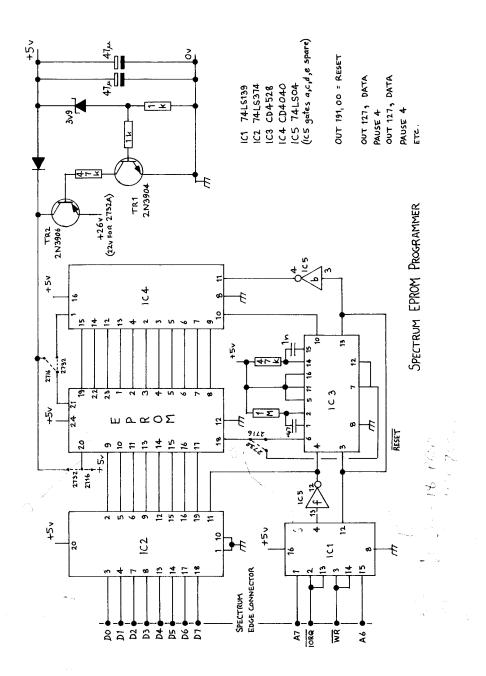

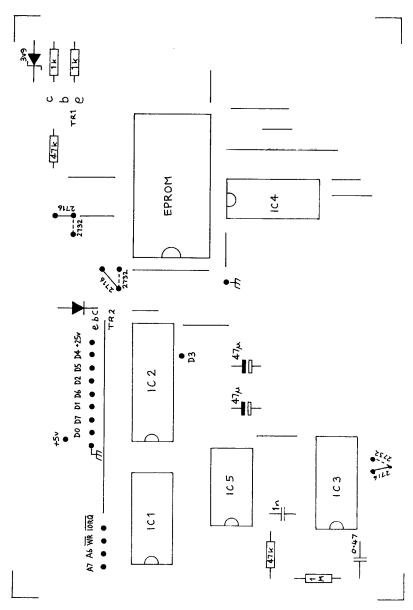

Spectrum E Prom Programmer

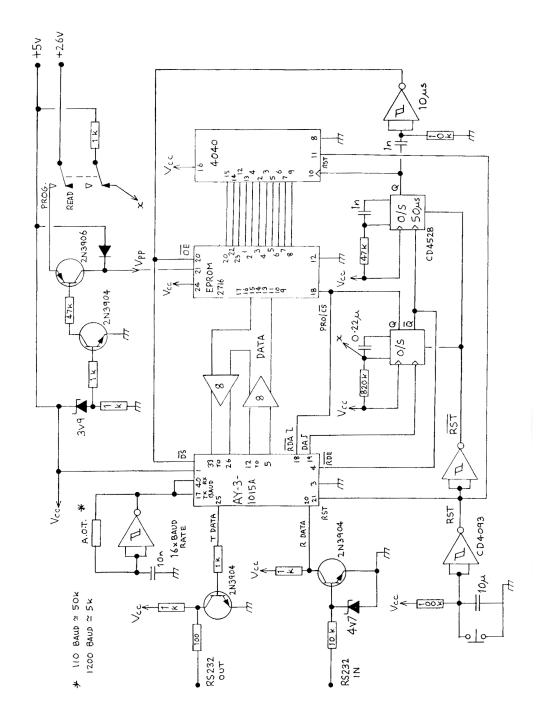

RS232 E Prom Programmer

Spectrum Freezer

Teletron

Teletron VDU

Ham Text

## **PREFACE**

This publication covers a very wide range of Television Projects and pays particular attention to the role the home computer can play in Television. The projects range from the simple to the advanced, with a range of printed circuit boards being made available to ease any constructional difficulties. All the software featured has been specially written and lots more is in the pipeline and will be made available via CQ-TV the B.A.T.C.'s quarterly publication.

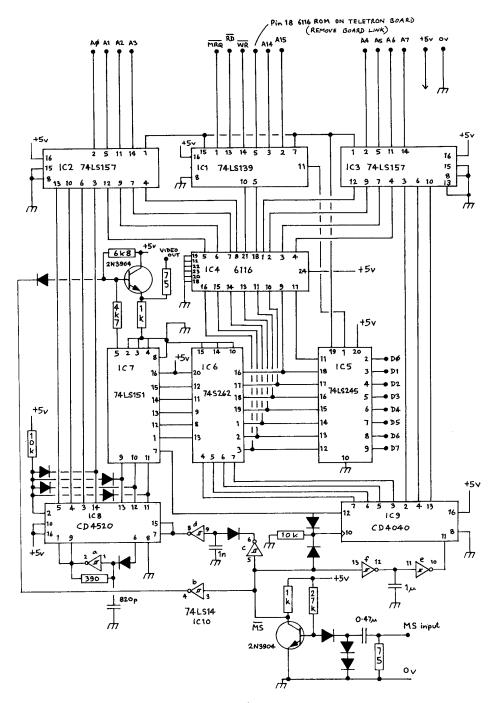

Teletron is an attempt at launching a very flexible micro controller card for use in Television applications. It is hoped to support this card with plug in software and plug in modules, the accompaning VDU is designed to work with a feed of mixed sync for locking purposes and will not function without.

This publication also incorporates the popular Electronic Test Card and PAL coder from the original and no longer produced Amateur Television Handbook. A Secam Coder designed by Jacques Pochet has also been introduced for which a plug in Printed Circuit Card is available from him, this module is pin compatible with the PAL Coder and enables Secam operation by a simple module change.

Time scale is always a problem when putting together a publication like this and one problem which has developed is a Texas chip the 74S262 which was new at the outset and seems to be becomming scarce, should this problem not resolve itself then alternative Engineering will be introduced. Please contact Members Services for any such supply problems.

I hope you will all find Micro and Television Projects an interesting and stimulating publication.

TREVOR BROWN

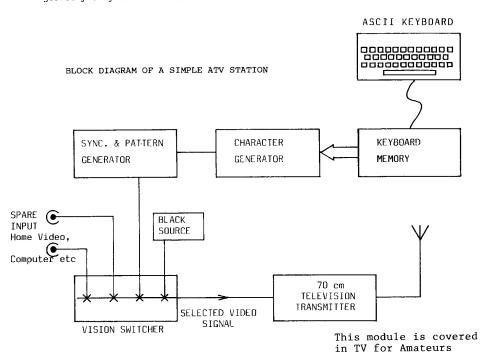

# QCB PRT CHAPTER 1 A SIMPLE ATV STATION

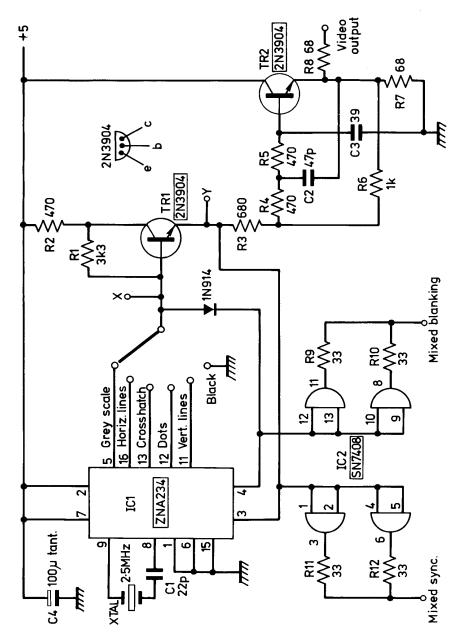

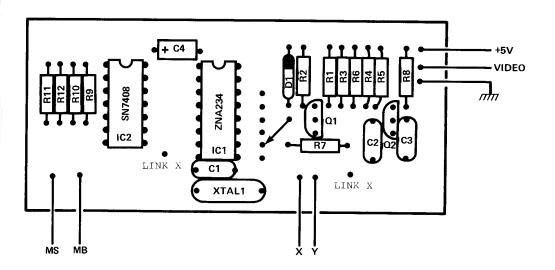

### **TEST PATTERN & SYNC GENERATOR**

This is the first module in our simple TV station and is the 'heart' of the system, providing the master timing signals to which the rest of the picture sources are synchronised. It also provides the TV test waveforms which are essential for checking out and setting up the rest of the station.

Of these waveforms the most useful is the grey scale or 'staircase' signal, which is used to measure the linearity of video processing circuits. The crosshatch or grille is also useful, particularly for checking the geometry of your TV monitor and receiver.

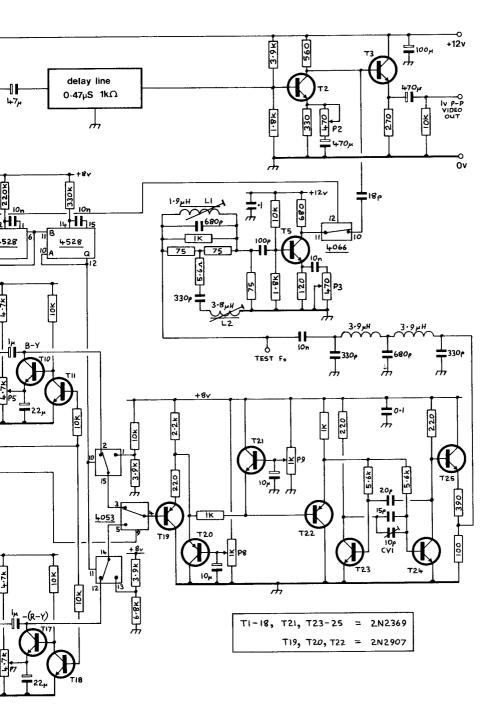

FIG. 1. 625 line t.v. pattern and sync generator.

The circuit revolves around the Ferranti Pattern Generator IC, ZNA 234. All the waveforms required are generated within the chip, though for some reason known only to Ferranti they are not processed with mixed blanking, which is, however, available on the chip. Ferranti also generate the grey scale waveform upside down, i.e. it is a falling staircase, not a rising one as convention dictates. In order to keep the circuit as simple as possible this has not been changed, and its sense is unimportant for adjusting an amateur TV station.

The ZNA 234 requires a 2.5 MHz crystal oscillator, and all the electronics for this are within the chip. The crystal itself is connected between pins 8 and 9 and requires a small 22 pF capacitor in series with pin 8 (C1). The value of this capacitor can be varied to adjust the line speed of the generator.

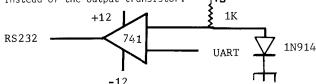

The TV waveforms produced from the chip require 'holes' cut in them so as to accommodate the pulse information which is essential to a TV transmission in order to start the line and field scan generators of the receiver at the correct time. These gaps for the sync pulses are produced by a mixed (line and field) blanking signal which turn on the 1N914 diode and turns off TR1, so as to suppress the video signal.

It would appear to follow from the circuit diagram that by turning off TR1 we would also turn off TR2, but things are not always what they seem; both pin 3 and pin 4 of the ZNA 234 are returned to the +5V rail by 3K3 resistors within the chip.

The next stage is to add sync pulses to the waveform. This is done by using the mixed sync output to turn TR2 off. You can do this by reducing its base potential below the limit set by the internal pull-up resistor on pin 3 and R3 R6 R7.

The sync pulses are narrower than the blanking pulses and are offset slightly to cause two holes in the picture, one before the sync pulse (called the front porch) and one after (back porch). The timings and levels of the various signals are shown, should an oscilloscope be available for viewing the signals. The output of TR2 is low impedance and a series resistor is included to restore the output impedance to 75 ohms. This output must be terminated in a 75 ohm resistor before measurements are taken. C2 C3 R4 and R5 are part of a low pass filter to stop any out of band transients reaching the video output. If the generator is required only for TV service work and not to drive a transmitter then they can be omitted.

IC2 is not essential to the working of the pattern generator, its purpose being to buffer the outputs and provide blanking and sync pulses at at standard level of 2V peak to peak when terminated in 75 ohms. These signals are useful for controlling other video equipment, but for a stand-alone pattern generator IC2 may be omitted.

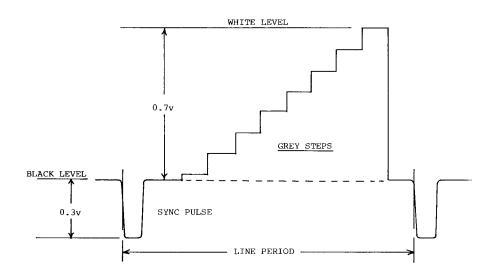

BASIC GREY-SCALE WAVEFORM

# PCS PROJECTE CAPTION WRITER

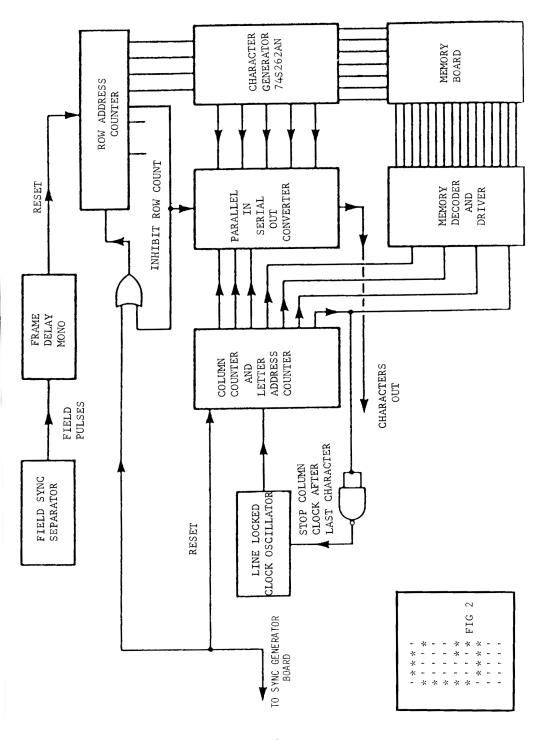

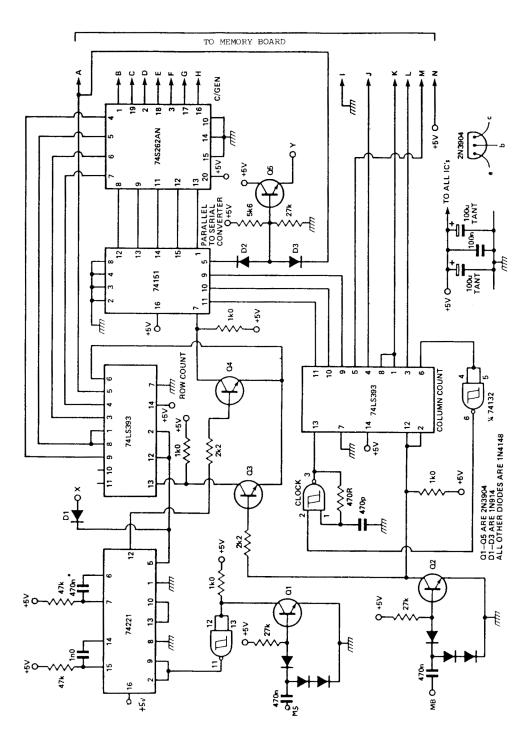

One use for the 2V mixed sync and blanking pulses is to drive an electronic character generator which gives you the ability to type 16 character messages superimposed on our test waveforms.

The 2V mixed sync pulses are fed into a window clip circuit which slices the centre section of the pulses and converts them into TTL level signals. The positive going edges of the sync pulses cause one half of a dual monostable to trigger for an unstable period given by its time constants 47K x 1n where C x R = 0.7T, i.e. about 33 microseconds. During the period when this monostable is unstable it allows the second half of the dual monostable to be triggered by a negative transition (this should happen only at the end of a frame scan when the equalising pulses are present).

At the end of the unstable period of the second monostable we start the character generator. The vertical position of the characters in the frame can be varied by adjusting the value of time constants associated with that monostable. The 47K resistor marked \* can be decreased in order to move the characters up the screen.

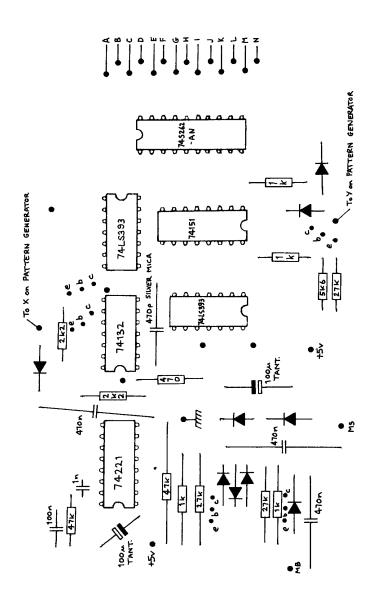

Now we have positioned the characters on the TV frame we must consider how to generate them. Figure 2 shows a typical character, which is produced within the constraints of a matrix of 5 vertical columns and 9 horizontal rows. Producing the letters and figures is a 74S262AN integrated circuit. There are 128 characters available within the chip, each individual one being selected by a code supplied to connections B C D E F G H of the chip. The particular legend required is stored in memory elsewhere on our character generator board.

The horizontal direction of the character matrix is scanned by the column counter, which runs at 5 x 16 x line speed, i.e. 5 columns x 16 characters for each line. After each of the five columns the generator is ready to receive the next character designation from the memory board; this information is carried on lines leading to pins J K L M (4 bit code, 16 locations). The 74S262AN supplies all five of its columns at the same time (parallel data). The column address is used to select one column at a time and this is handled by the 74151. The column counter is driven from a clock oscillator, which is synchronised to a feed of mixed blanking pulses.

The row selection is carried out within the 74S262AN. Pins 4 5 6 7 carry this code, which is derived from a row counter driven by the line rate pulses. Every four lines the character generator jumps to the next row.

The TTL signal corresponding to the characters is available at the output of the 74151 and is blanked and fed out via TR5.

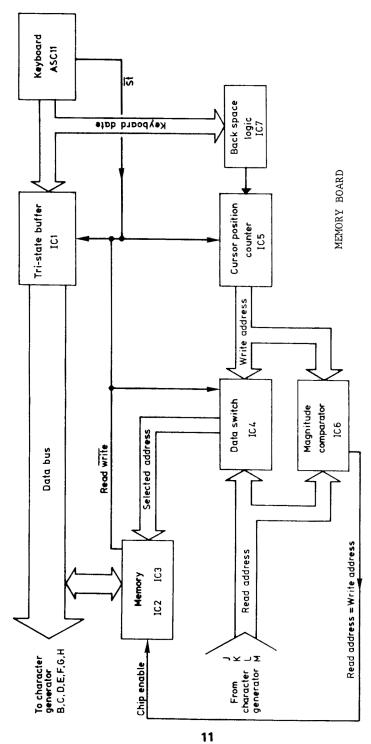

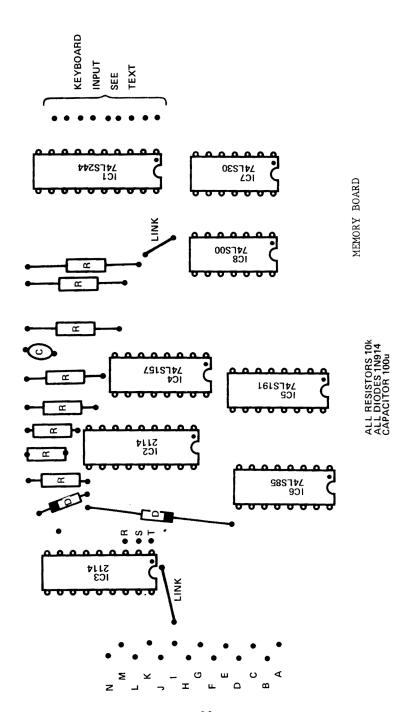

### MEMORY BOARD

The pins J K L M carry a four bit address code from the character generator which changes every time a different character is scanned. The information in that particular memory location is then available to the data bus.

The next stage is to be able to determine the content of this memory, which is in fact RAM (random access memory). To do this we need to connect a keyboard to the data bus. An ASCII keyboard has seven data outputs and supplies a code to these outputs dependent on which key is pressed. The keyboard also provides a short pulse called the 'strobe' every time a key is pressed to indicate that the keyboard is sending data. This strobe pulse can be 'active high' or 'active low' and most keyboards provide both. Our circuit requires active low, designated ST with a line above the letters. When this signal occurs the outputs of IC1 (74S244), which are normally floating, assume the same state as the inputs and thus feed the keyboard output to the data bus. The stobe pulse also passes to the RAM where pin 10 of the memory chips (2114) is driven low. This puts them into a 'write' mode, enabling the data to be stored.

The next task is to control where the keyboard data is stored. By inserting IC4 in the address lines to the RAM we can switch these address lines in the write mode. IC4 (74S157) is a four bit data selector and functions just like a four pole double-throw switch, in that when pin 1 is driven low the RAM address lines are fed from the QA QB QC QD outputs of the counter chip IC5.

The write address is stored in IC5, a counter which counts up to 16 and then resets. By using the strobe pulse to advance it, its count will increase by one every time we press a key, ensuring that the selcted letter is stored in the next location in memory. When IC5 has been clocked to location 16 it will automatically reset to character location 1.

The next stage is to display a 'cursor' so that we can see the next location to be typed into on the screen. To do this we compare the read and write addresses in the four bit magnitude comparator IC6 (74LS85). When the two addresses are the same (i.e. the character generator is scanning the next location for typing) the output of the comparator, pin 6, goes high. This high state is connected to pin 8 of our RAM which is the chip enable pin (active low), so when our two addresses are identical the RAM is disabled. This causes the data bus to be pulled high by the 10K pull-up resistors and ensures that the data bus assumes a high state in the absence of data. If all the data bus bits are high then our caption writer will produce a white block, which makes an excellent cursor.

The full ASCII code provides many things besides letters and numbers, including cursor functions such as Backspace, Delete and Cursor Home. In order to keep this circuit simple these functions have not been decoded except code 7F (keyboard outputs 1111111 if you prefer): this is the Delete code. IC7 (74LS30) is an eight input NAND gate with seven of its inputs

MEMORY BOARD

looking at the keyboard output. Now when the delete code is presented by the keyboard the output of IC7 will be low. This signal is inverted and fed into the counter, with the following effect: when the counter is clocked by the strobe pulse it will count down instead of up. The output signal of IC7 is also used to inhibit the write signal to the RAM, so the cursor will step back and the information in the RAM will remain unchanged.

In effect we have created a backspace function, probably the most useful cursor function for a small character generator. The use of the Delete key for this function instead of the backspace key simplifies our circuit and does not cause too much operator confusion as keys like this are rarely used in a touch-type mode.

Switch S1 is used to remove the cursor; closing it inhibits the chip enable input of the RAM from going high, the state which generated the cursor. The page switch is optional and if not required pins 1 2 3 of the RAM should be connected to ground. Note that provision is not made on the PCB for the three 10K pull-up resistors associated with this switch. These are best fitted directly to the back of the switch.

All that remains is connecting up a keyboard, and on the prototype a RCA model CP601 was used. The output is via a PCB mounted socket, which takes a 3M connector no. 3421-6020. Pin numbers for this particular keyboard are shown on the circuit diagram. If you use another ASCII keyboard note that the strobe required is active low. Data lines are connected to pins 11 8 4 13 15 2 6 of the 74LS244 in that order, with pin 11 being the least significant bit.

# PCB PROJECT SIMPLE VISION SWITCHER

With the electronic vision switcher we can select which of any four video signals is routed to the transmitter. Our electronic test generator can be one of the sources, with a camera and home computer as other inputs.

Figure 1 shows the circuit of the switcher. The four video inputs are fed to the base of four single transistor amplifiers, all sharing a common 470 ohm load. The transistors are switched on and off at their emitters - to switch on any one of the four transistors we simply take its emitter down to logic zero. The video signal then present at its base will appear inverted across our common load resistor and pass to a two stage amplifier, where it is re-inverted and fed to the video output.

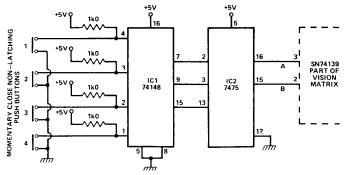

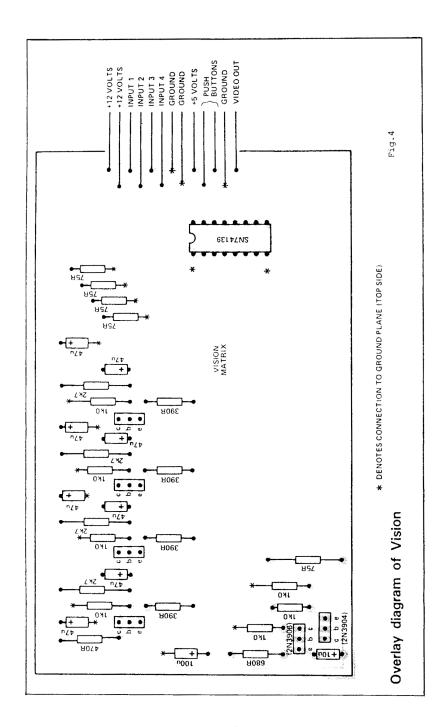

The logical zero states required at the emitter are supplied from an SN74139 IC. This chip will allow only one of its outputs to assume logic 0 at any one time. The 74139 is fed with a two wire logic signal from a push button selector.

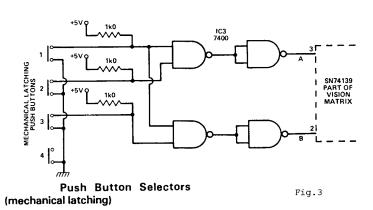

Figure 2 shows a push button selector using momentary contact switches. The buttons are designated using a priority encoder, the information being retained in the 7475 latch. Figure 3 shows a simpler system using the mechanical latching type of press buttons.

The PCB layout is depicted in figure 4; the ground plane is on the component side. Only the circuitry of fig. 1 is assembled on the PCB as it is envisaged that the push button coder chips would be mounted adjacent to the switches.

The push button codes generated should be

Button one: A logic 0, B logic 0.

Button two: A logic 0, B logic 1.

Button three: A logic 1, B logic 0.

Button four: A logic 1, B logic 1.

# CQ-TV MAGAZINE HAS NEVER BEEN BETTER. MAKE SURE OF YOUR REGULAR COPY BY JOINING THE BATC NOW

SEND A 9" x 6½" STAMPED, SELF?ADDRESSED ENVELOPE FOR FURTHER DETAILS AND A MEMBERSHIP APPLICATION FORM TO:

DAVE LAWTON.

"GRENEHURST",

PINEWOOD ROAD.

PINEWOOD ROAD, HIGH WYCOMBE, HP12 4DD

SWITCHER CIRCUIT DIAGRAM

Push Button Selectors (momentary contact)

Fig.2

# CHAPTER 2 CHAPTER 2 THE BEST OF THE HANDBOOKS

## **ELECTRONIC TESTCARD**

#### INTRODUCTION

This unit was designed to provide an electronically generated test pattern to replace the conventional test-card/camera combination. The concept is not, of course, original; the familiar Philips PM5544 test card has been with us for some years now and many broadcasters have designed similar units for their own use. No particular merit for originality is claimed for this design except that it is simple and cheap enough for the average amateur to tackle.

### **FACILITIES**

The generator requires an input of standard mixed-sync and mixed-blanking pulses plus a 5 volt power supply, and provides RGB outputs suitable for feeding to a colour encoder. The general appearance of the test card can be seen from the photograph although it is reproduced here in black and white. It is not as comprehensive as its commercial counterparts but does include the most important features needed for evaluation and adjustment of colour monitors, etc, these are as follows:

CROSSHATCH for linearity and convergence tests including a special central pattern for static convergence.

CASTELLATIONS for setting picture size.

A CIRCLE for aspect ratio and linearity tests.

GREY-SCALE and COLOUR BARS for video and coder adjustments.

MULTIBURST for focus and high frequency response.

LETTER BOX for low frequency response (smearing).

RED/WHITE alternate bars for testing chrominance/luminance delay.

In addition to the composite test card, individual full-screen waveforms can be selected by means of an optional thumbwheel switch. These are:-

Field square-wave (50 Hz).

Multiburst (1.25 to 6.67 MHz).

Red/white bars.

Grey scale.

Colour bars (100%).

Peak white.

Black.

Line square-wave (15,625 Hz).

Cross-hatch (white on black).

Note that because of the masking effect of the circle, the multiburst part of the composite test card covers the frequency range 1.5 to 5 MHz.

### GENERAL DESCRIPTION

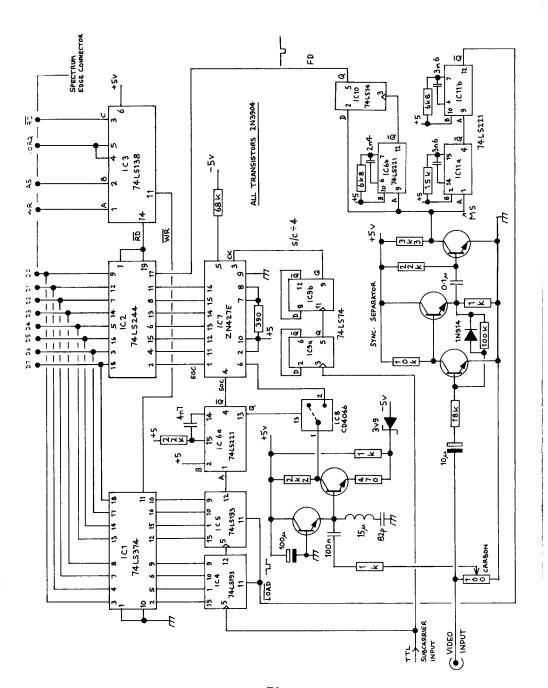

The unit is split into three functional blocks, each of which occupies a standard sized, double sided printed circuit board.

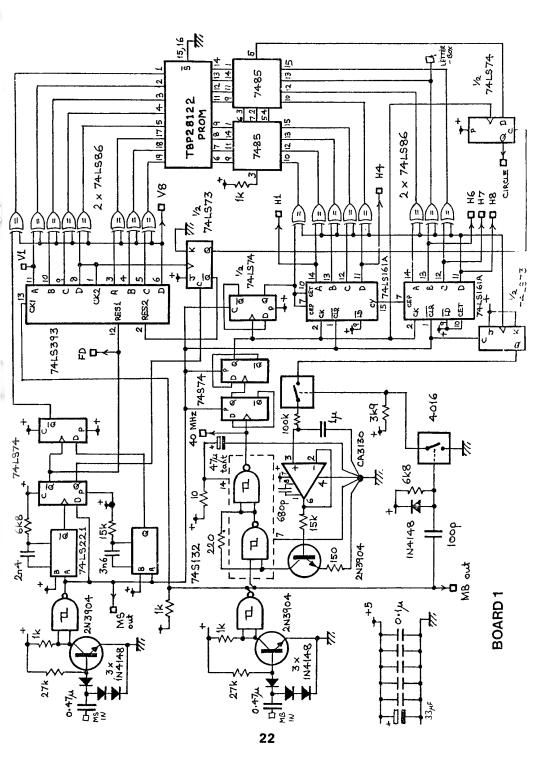

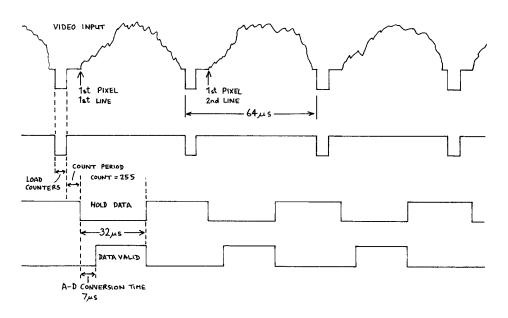

Board-1 is the timing generator which accepts mixed syncs and blanking and generates a line-locked clock at approximately 40MHz (which is divided down to give various horizontal waveforms) and derives field and line drive pulses. This board also contains the circle generator which uses a PROM to store the circle shape information.

Board-2 generates the cross-hatch, multiburst and castellation waveforms by counting and gating together pulses from board 1: Board-3 combines and selects the various signals from the other two boards and produces the required RGB outputs. It would be a simple matter to adapt the final pattern to suit individual requirements, for example an electronically generated callsign could replace one of the patterns within the circle.

### CICUIT DESCRIPTION - BOARD-1

The mixed sync and blanking inputs (standard 2v p-p) are first converted to TTL levels by the transistor and diode input circuits. The arrangement adopted results in the input signals being 'sliced' at a level of approximately twice the voltage dropped across a diode from their positive excursion, this being about right for 2v p-p pulses. If a non-standard pulse amplitude is used some experimentation may be required; any disturbance or glitches in the TTL syncs and blanking waveforms can wreak havoc in the digital circuitry.

The TTL sync signal is fed to two monostables, one with a priod of approximately 11uS and the other 37uS, the output of the latter being a line frequency square-wave with half-line information removed. The output of the first monostable clocks a D-type flip-flop which has syncs fed to its D input, the result being that the Q output is normally 1 but during broad pulses it changes to 0, in other words, the output of the flip-flop is field drive. The field drive in turn clocks another D-type which this time has a 37uS monostable output fed to its D input. Because on one field the first broad pulse occurs during the first half of a line, and on the other during the second half, the flip-flop output consists of a 25Hz picture rate square wave.

The TTL mixed blanking signal enables a 40MHz oscillator consisting of a schmitt-trigger gate with feedback from output to input. A schottky device must be used here because a standard speed gate will not oscillate at 40MHz. It will be noticed that the usual capacitor from the schmitt input to ground is absent, and is replaced by a transistor! This transistor, along with stray capacitance allows the oscillator frequency to be varied so as to maintain the period of the oscillator at exactly one 2048th of the active line period (approx 52uS). Line locked oscillators are notoriously troublesome in their somewhat conflicting requirements of accurate frequency stability and precise phasing with respect to syncs. The novel approach adopted here is to separate these requirements by using a hard-gated oscillator to ensure good phase stability plus a slow-acting frequency control loop to keep their period correct. Obviously this does result in an oscillator which is sensitive to short term disturbance as is a free running oscillator, so extreme care must be taken not to couple noise or transient signals into it. In practice single

point earthing has been found desirable plus local decoupling of the oscillator supply as shown on the circuit. It may be necessary to add a small capacitor (up to 10pF) from ground to the schmitt input.

The 40MHz clock is divided by 4 in the 74S74 to give a gated 10MHz clock (actually 9.86MHz) which feeds the horizontal counter. This consists of half of a dual D-type flip-flop plus two 4-bit synchronous counters, giving nine bits in all. The counter outputs follow a binary sequence of 0 to 511 from left to right across the television line. The most significant bit (MSB) of this counter is used to clock a J-K flip-flop on its negative transition. If the oscillator frequency becomes less than it should be there will be less than 512 clocks to the 9 bit counter during the active line period and the most significant bit will never be clocked back to zero. If however the frequency becomes high then the MSB will be clocked to zero before the end of the line. In the first case, therefore, the 74LS73 flip-flop output will remain low whereas in the second case it will be clocked high near the end of the TV line. The state of this flip-flop is sampled just at the beginning of the line blanking by means of the CMOS analogue switch (4016) and controls the charging/discharging of the 1uF capacitor. The voltage across this capacitor is monitored by the CA3130 FET input op-amp and determines the oscillator frequency. In this way the frequency is stabilised at the correct value. Several copies of this circuit have been made and it has been found to be very reliable.

The mixed blanking signal is also used to clock the 8-bit vertical (line) counter 74LS393. By means of the other half of the 74LS73 dual flip-flop, the most significant bits of this counter are held to zero until after the first sixteen lines following field blanking. As the number of active lines is 288 (which equals 256+32) this results in the vertical count of 0 to 255 being accurately centred in the picture. Because of the interlaced line structure, spacially adjacent lines are in fact in opposite fields. From a spacial point of view, therefore, the 25Hz picture square wave represents the least significant of the vertical sreen address, and is used as such. What we have then is a horizontal count and a vertical count, both running from 0 to 511, correctly centred in the active picture area. From these signals most of the waveforms needed for the test card can be derived.

The circle generator works on the principle of storing in a PROM the values of the horizontal co-ordinates of the edge of the circle for each TV line, that is it stores the values for X=SQR(RxR-YxY), one form of the equation of a circle of radius R. From what has been said, it might be thought that we need a value in the range 0 to 511 for each of 512 lines. However PROMs do not come with 9 bit outputs so it is fortunate that we can reduce this to 8 bits by taking advantage of the symmetry of the circle. The procedure adopted is to feed the 8 least signicant bits of both vertical and horizontal counts each into an exclusive-OR gate. The other inputs of the 8 vertical XOR gates are commoned and fed to the most significant bit of the vertical count and similarly the horizontal ones are connected to the most significant horizontal bit. In effect, we have arranged that counts 0 to 255 are unaffected (the XOR gates acting as non-inverting buffers) whereas counts 256 to 511 now become 255 to 0 on the exclusive-OR outputs because the 8 bits are inverted. We now have vertical and horizontal addresses which accurately reflect the symmetry of the circle and the PROM need hold only one quadrent's worth of data (256 eight bit words).

The modified vertical address is fed to the address inputs of the PROM, whose outputs now give the correct horizontal coordinate for the edges of the circle (note that the aspect ratio has been taken into account when calculating the PROM contents). All we need to do to actually generate the circle signal is to compare the PROM outputs with the modified (reflected) horizontal count; when the count exceeds the PROM data then we are inside the circle, otherwise we are outside! To this end, two 7485's are wired as an 8-bit comparator whose output is de-glitched by the remaining D-type flip-flop to provide a clean circle.

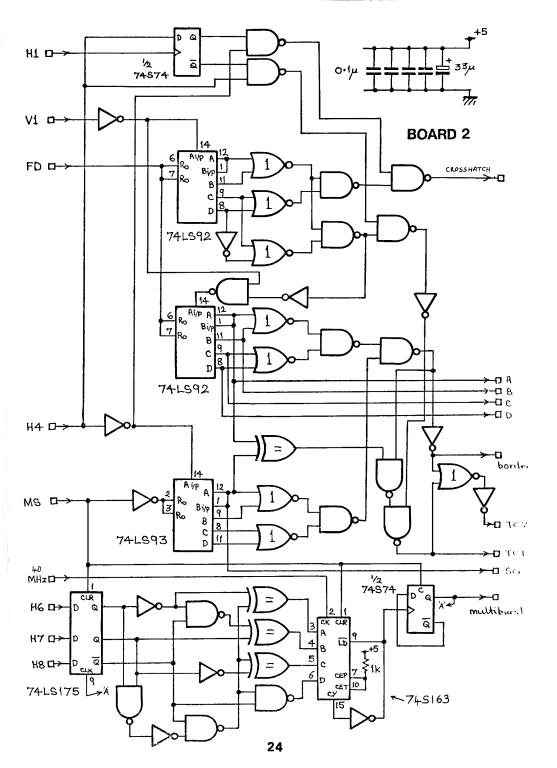

### CROSSHATCH & CASTELLATION - BOARD-2

The waveforms produced on board 1 are not directly suitable for producing the crosshatch and castellation signals (which we will call the 'basic test-card') for two reasons; firstly we want the test-card squares to be truly square! Because of the aspect ratio, and the choice of horizontal clock frequency, a rectangle of say 16 lines by 16 clock pulses is not a square. With an aspect ratio of 4:3 we will get squares if we divide the screen into 16 (horizontal) x 12 (vertical) parts. We cannot easily derive the appropriate vertical waveform from the counter on board 1, so instead an additional divide-by-2 counter on board 2 is used clocked from the least significant output of the vertical counter on board 1 (shown as V1 on the circuit). This results in an overall division factor of 24 (12x24=288). The divide-by-16 horizontal waveform is already available on board 1 so what is the other problem? We want to produce an all-round castellation, but the size of the squares is too great to do this by having a central area of 10 by 14 squares and a one-square-thickness border all round. Rather, the ideal is to have a 15 by 11 central region with a half thickness border. This is what the second 74LS92 and the 74LS93 achieves. The arrangement adopted results in the second 74LS92 having a zero count during the top and bottom borders and the second 74LS93 having a zero count during the left and right borders. It is a simple matter to gate these signals together to produce a composite "border" signal. castellations, we must use this border signal to enable a "chequerboard" pattern - this is easily generated by gating together suitable horizontal and vertical square waves in an exclusive-OR gate (centre of circuit).

All that is now needed are two crosshatch patterns. One to form the dividing lines between the test-card squares (the lines are white and the squares grey) and the other two for the central static convergence pattern. It may not be obvious why two crosshatches are needed; for static convergence there must be a "cross" at dead centre, whereas the test-card one does not provide this - it is offset in both vertical and horizontal directions. The horizontal components of the two crosshatch patterns are derived by gating together the outputs of the first 74LS92, resulting in horizontals 4-lines (per picture) thick. The vertical components are obtained by means of the D-type flip-flop at the top of board 2 circuit diagram and when combined with the horizontals give the required crosshatch signals. The crosshatch which forms part of the "basic test card" is gated with the castellation and the border signals to form the component signals of the test-card (TC1 and TC2 on the circuit).

### MULTIBURST - BOARD-2

The multiburst signal is derived by feeding the main 40MHz clock into a programmable divider whose division ratio is changed in eight steps across the active line. A square-wave output is required so the division factors must all be even. The factors chosen are:

32 1.25 MHz 26 1.54 MHz 20 2.00 MHz 16 2.50 MHz 12 3.33 MHz 10 4.00 MHz 8 5.00 MHz 6 6.67 MHz

As mentioned earlier, the first and last are only available when the full-sreen multiburst is selected. A 3-bit horizontal address (H6, H7, H8) is taken from board 1 and latched by the 74LS175. It must then be converted into a four-bit code which, when fed to the preset inputs of the 74S163 divider, results in the required division ratios (in fact half the values given above because there is a subsequent divide-by-two stage). This is the function of the network of gates between the 74LS175 and the 74S163. If you care to work it out you should find that the correct code conversion is carried out, bearing in mind that the H8 output from the latch is inverted and that in fact the complement of the division ratio is required.

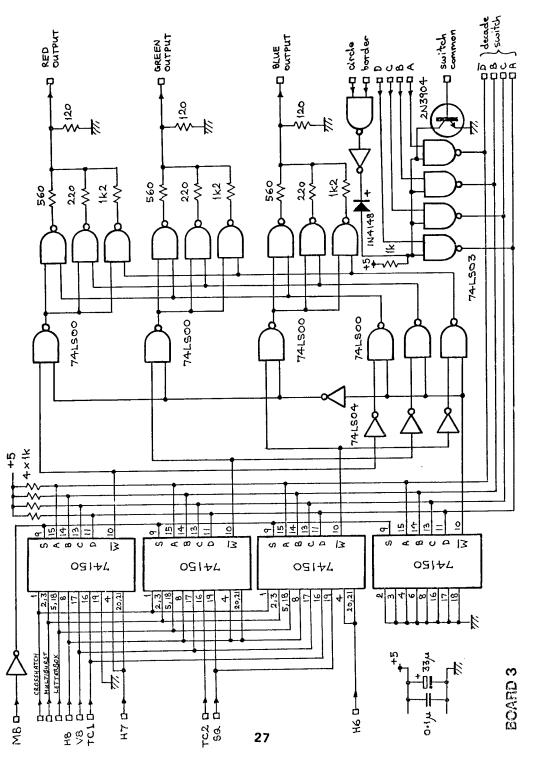

### PATTERN SELECTOR & OUTPUT - BOARD-3

This board has the simple job of selecting the required patterns to the correct parts of the screen, and of providing the RGB outputs. There are fourteen possible combinations of outputs - eight luminance values, from black through grey to white (R=G=B), plus the six saturated colours obtainable from the primaries (red, green, blue, yellow, cyan, magenta). The output stages consist of TTL stages resistively matrixed together so that each output, when terminated in 75-ohms, can take up a voltage between 0v and 0.7v in steps of 0.1v. The output circuitry is fed from four TTL lines; one selects monochrome or colour and the other three select either one of eight luminance values or one of the colours. Both black and white are obtainable either when "monochrome" or "colour" is selected, and advantage is taken of this to slightly simplify the selection circuitry.

The four bits controlling the output stages are fed from four 16 to 1 line multiplexers (74150) which have the various pattern signals from boards 1 and 2 fed to their inputs. When a full-screen pattern is selected the thumbwheel switch data is simply fed to the multiplexer address inputs. The circuit is arranged so that, using a decade thumbwheel having true and inverted outputs wired as shown, positions 0.through 7 and 9 select the nine patterns listed earlier. When the switch is at position 8, the common becomes open circuit and the 2N3904 turns off, thus allowing the A-D vertical select lines (from board 2) to control the multiplexers when the circle signal corresponds to "inside". When the circle is set at 0 ("outside") the multiplexers receive an address of 1111 which selects the "basic test card" to the outputs, the result being the full test-card display as shown in the photogragh. By re-arranging the inputs

to the 74150's many different effects can be achieved, but bear in mind that some inputs are used only in the test-card (e.g. letter box) and others only for full screen patterns (e.g. field square wave V8).

### CONSTRUCTION & TESTING

A set of three double-sided printed circuit boards, as well as a pre-programmed PROM, are available from BATC 'Members Services'. The current issue of CQ-TV magazine should be consulted for details.

The boards come complete with layout diagrams which should be followed carefully. Experience has shown, now that a great many test cards have been built, that in almost every case where trouble is experienced, the constructor has failed to solder those components which act as 'through stakes' for the board, on BOTH sides. If trouble is encountered it is strongly recommended that a very thorough examination of the solder points be made.

No serious problems should be encountered in getting the generator to work as long as good high-speed logic construction techniques are adopted throughout. Take particular care with decoupling and earthing. Trouble spots, if any, are likely to be the 40MHz oscillator on board 1 and the multiburst divider on board 2. Feeding a 40MHz TTL signal along more than an inch or two of wire can be tricky, and you may find it helps to add a small series resistor at the sending end to absorb reflections.

A useful tip is to temporarily disconnect one of the pattern inputs to board 3 and instead connect a flying lead to the 74150. If you select this input with the switch, you have a ready made probe which can be used to monitor signals within the generator on a TV screen. Mixed line and field rate signals, meaningless on an oscilloscope, are made instantly recognisable by this method.

TBP28122 PROM for test-card generator.

(Hexadecimal notation)

0010 FO EA E6 E2 DF DB D9 D6 D4 D1 CF CD CB C9 C7 C6 0020 C4 C2 C1 BF BE BC BB B9 B8 B7 B5 B4 B3 B2 B0 AF 0030 AE AD AC AB AA A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 9F 0040 9E 9D 9C 9C 9B 9A 99 98 97 97 96 95 94 94 93 92 0050 92 91 90 8F 8F 8E 8D 8D 8C 8B 8B 8A 8A 89 88 88 0060 87 87 86 85 85 84 84 83 83 82 82 81 81 80 80 7F 0070 7F 7E 7E 7D 7D 7C 7C 7B 7B 7A 7A 79 79 79 78 78 0080 77 77 76 76 76 75 75 74 74 74 73 73 73 72 72 71 0090 71 71 70 70 70 6F 6F 6F 6E 6E 6E 6E 6D 6D 6D 00A0 6C 6C 6C 6B 6B 6B 6A 6A 6A 6A 69 69 69 69 68 68 00B0 68 68 67 67 67 67 67 66 66 66 66 65 65 65 65 0000 65 64 64 64 64 64 64 63 63 63 63 63 63 62 62 0000 62 62 62 62 62 61 61 61 61 61 61 61 61 61 60 00E0 60 60 60 60 60 60 60 60 60 60 60 60 5F 5F 5F

#### **ADDENDUM**

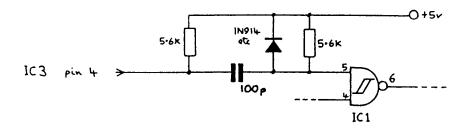

Since this circuit first appeared in BATC handbook-1, John Sager G80HN, noticing a small jitter problem associated with the multiburst signal, found that by applying a clock pulse to IC19 during the reset pulse an improvement could be affected. The following circuit may be used to accomplish this although some modification to the PC boards are necessary.

Break the track between Pins 4 & 5 of IC1 (board-1) and wire in the components as shown, this generates a pulse on the 40MHz clock line shortly after the begining of the line sync pulse to reset IC19.

The jitter problem is caused because the 74S163 in the original cicuit is never reset, and the counter is left with one of the three consecutive counts from the previous line, which vary randomly due to the operation of the phase lock circuit for the 40MHz oscillator. Thus the multiburst can start 25nS early or late.

### TEST CARD PARTS LIST.

| BOARD-1                                                         | DOADD 2                       |

|-----------------------------------------------------------------|-------------------------------|

|                                                                 | BOARD-2                       |

| 2 off 7485                                                      |                               |

| 1 off 74LS73                                                    | 4 off 74LS00                  |

| 2 off 74LS74                                                    | 2 off 74LS02                  |

| 4 off 74LS86                                                    | 2 off 74LS04                  |

| 2 off 74LS161A                                                  | 1 off 74LS86                  |

| 1 off 74LS221                                                   | 2 off 74LS92                  |

| 1 off 74LS393                                                   | 1 off 74LS93                  |

| 2 off 74LS161A<br>1 off 74LS221<br>1 off 74LS393<br>1 off 74S74 | 1 off 74LS175                 |

| 1 off 74S132                                                    | 1 off 74S74                   |

| 1 off TBP28122 (PROM)                                           | 1 off 74S163                  |

| 1 off CD4016                                                    |                               |

| 1 off CA3130                                                    | 4 off 100n ceramic disc       |

| 1 0/1 0/10/03                                                   | 1 off 33uF 6.3v electrolytic  |

| 3 off 2N3904                                                    |                               |

| 7 off 1N4148                                                    | 1 off 1K <del>1</del> W       |

| 7 011 111115                                                    |                               |

| 2 off 0.47uF polyester                                          |                               |

| 1 off 1uF polyester                                             |                               |

| 1 off 1uF polyester<br>1 off 2n4 polystyrene                    | BOARD 3                       |

| 1 off 3n6 polystyrene                                           |                               |

| 1 off 680pF polystyrene                                         | 4 off 74LS00                  |

| 1 off 100pF ceramic                                             | 1 off 74LS03                  |

| 5 off 100nF ceramic disc                                        | 1 off 74LS03<br>1 off 74LS04  |

| 1 off 33uF 6.3v electrolytic                                    | 4 off 74150                   |

| 1 off 47uF 6.3v tantalum                                        |                               |

| 1 011 4701 0.5V cantalum                                        | 1 off 2N3904                  |

| 1 off 10 ohm                                                    | 1 off 1N4148                  |

| 1 Off 150 ohm                                                   | 1 311 111111                  |

| 1 off 220 ohm                                                   | 1 off 100n ceramic disc       |

| 2 off 1K                                                        | 1 off 33uF 6.3v elecrolytic   |

| Z 011 1K .                                                      | 1 011 0001 0107 01001019      |

| 1 off 3.9K                                                      | 3 off 120 ohm                 |

| 2 off 6.8K                                                      | 3 off 220 ohm                 |

| 2 off 15K                                                       | 2 off 560 ohm                 |

| 2 off 27K                                                       | 3 off 560 ohm<br>5 off 1K     |

| 1 off 100K                                                      | AL LID C                      |

|                                                                 | 2 off 1 2V                    |

| all resistors ‡W                                                | 3 off 1.2K<br>all resistors ₩ |

# CARD MODULE

### PAL CODER

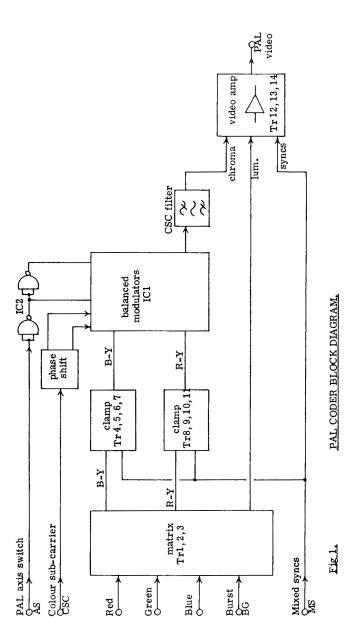

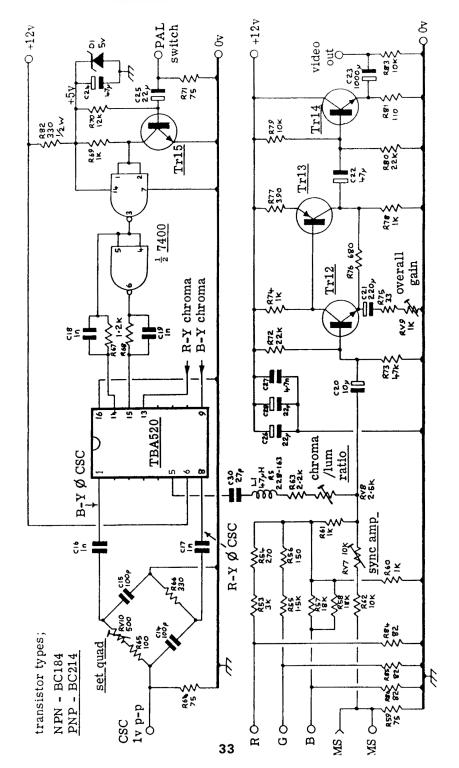

This encoder takes the basic red, green and blue colour signals and combines them with syncs and other necessary signals to produce a composite PAL colour video signal.

The unit has been made as simple as possible and features a single IC balanced modulator circuit, no complicated filter networks to adjust thus avoiding the need for luminance delay, single PC board, simple adjustment, single power supply requirements and low cost. This simplicity means that the residual carrier balance is outside professional broadcast standards though this is of little consequence to the amateur, and there is no bandwidth limiting of the chroma information. The harmonics of the colour sub-carrier frequency however have been reduced to acceptable levels with a simple filter.

### SPECIFICATION

INPUTS. a. Standard 0.7v non-composite RGB into 75 ohms.

b. Colour sub-carrier (CRC), 0.5 - 1v p-p into 75 ohms.

frequency 4.433 MHz.

OUTPUT. 1v p-p composite video across 75 ohms.

POWER SUPPLY. 10 - 12v dc stabilized.

### DESCRIPTION

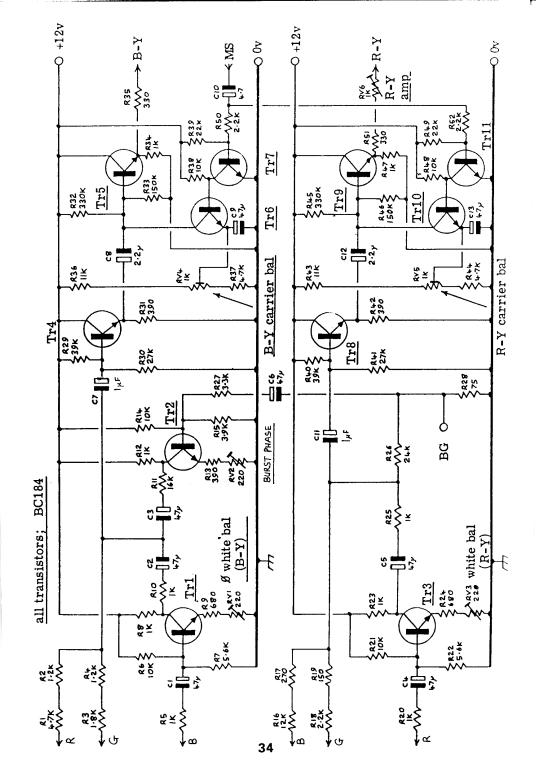

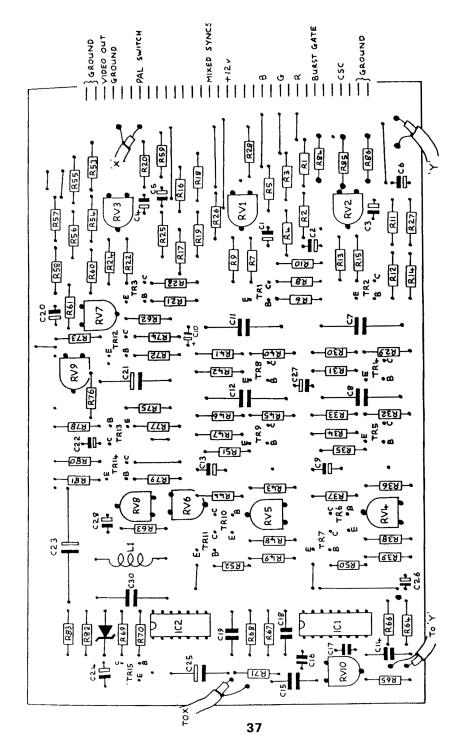

A block diagram of the PAL coder is shown in Fig 1. The coder uses a low-cost TV receiver decoder integrated circuit (IC1) in the "reverse" direction to code B-Y and R-Y signals into PAL video. The coder is a linear as opposed to a digital device and may be used for coding normal video signals from a camera, flying-spot scanner etc., as well as those from digital sources.

Red, green and blue video input signals are matrixed along with a burst gate pulse to give B-Y, R-Y and luminance signals as well as colour burst. Processing is done by TR1, 2 and 3 and associated resistor networks.

The B-Y and R-Y signals are a.c. coupled and need to be referred to a d.c. level before entering the balanced modulator IC1. Buffering and clamping, using mixed syncs, is carried out by TR4, 5, 6 and 7 for the B-Y signal channel and by TR8, 9, 10 and 11 for the R-Y channel.

IC1 accepts B-Y and R-Y signals, colour sub-carrier quadrature signals and axis switch (alternate line) signals. The output from IC1 consists of a full bandwidth PAL coded chrominance signal.

The last section of the coder adds the chromimance and luminance signals, together with the mixed sync signals, to provide a composite PAL coded signal at standard level. Gain setting and output stage are provided by TR12, 13 and  $^{14}$

It should be noted that in the interests of simplicity the colour signals exist at full bandwidth. A simple low Q filter is included between the modulator and the output amplifier to reduce the harmonic content to an acceptable level.

The PAL coder has been tested on colour bars and colour signals from a studio camera and gives very acceptable results on a vectorscope and subjectively when compared with a professional coder costing several thousand pounds!

#### CONSTRUCTION

The coder is built on a single sided PC board measuring 114 x 203mm, with connections brought out to the edge of the board making it suitable for plugging into a direct edge connector (0.1" spacing). The printed circuit board is available from BATC 'Members Services' department, details of which are to be found in the current issue of CQ-TV magazine.

In its original form, the TBA520 (IC1) was in the suffix 'Q' (QIL) version and had physically "staggered" pins. These should be carefully bent with pointed nosed pliers to convert it into a "dual inline" device. DIL sockets should be fitted for both IC1 and IC2.

#### SETTING-UP PROCEDURE

Setting up should preferably be done using an oscilloscope connected to the output although an alternative method using a colour monitor is also given.

Since the carrier balance is voltage sensitive it should be set up with the power supply which will be used in the finihed unit.

#### **PROCEDURE**

1. No input to R.G.B. Terminate output with a 75-ohm resistor.

Scope. Adjust CARRIER BAL RV4 and RV5 for minimum colour sub-carrier.

Mon/TV. Increase COLOUR SATURATION on monitor,

adjust RV4 for minimum blue/yellow tinting,

adjust RV5 for minimum red/cyan tinting,

repeat until neutral background is obtained.

2. Colour Bars to R.G.B. inputs. Short inputs together.

Scope. Adjust WHITE BAL RV1 AND RV3 for minimum colour sub-carrier.

Mon/TV. Adjust WHITE BAL RV1 to minimise blue/yellow tint,

adjust WHITE BAL RV3 to minimise red/cyan tint.

3. Remove R.G.B. short.

Scope. Adjust QUAD RV10 for minimum "twitter" on waveform when viewed at line rate with scope trigger control adjusted for "twitter" effect between alternate lines.

Mon/TV. Adjust QUAD RV10 for best saturation (look at red or blue bar).

4. Chrominance/luminance levels.

Scope. Adjust R-Y AMP RV6 for top of cyan bar envelope to equal top of yellow bar.

Adjust CHROMA/LUM RV8 for bottom of green bar to sit at black level.

Mon/TV. Switch off R and G guns of monitor,

adjust CHROMA/LUM RV8 for equal brightness of blue in white bar and blue bar positions. Switch off B gun, switch on R gun, Adjust R-Y AMP RV6 for equal red intensity in white bar and red bar positions. Return monitor to normal working.

- TV. First adjust saturation using normal off-air pictures, preferably colour bars. (bear in mind that there are 95% bars (BBC) or EBU bars (ITV).

Adjust as for monitor.

- 5. Overall gain and sync amplitude.

- Scope. Adjust SET OVERALL GAIN RV9 for 0.7v p-p video only, (ignoring sync amplitude).

Adjust SYNC AMP RV7 for 0.3v p-p sync, giving 1v p-p composite video.

- Mon/TV. Set SYNC AMP RV7 to mid-position, adjust SET OVERALL GAIN RV9 for maximum contrast consistent with no sign of clipping (colour changes in yellow bar).

- 6. Burst phase.

BURST PHASE RV2 is difficult to adjust without a vector scope, however the setting is not critical and could be set to mid-position.

Scope. Adjust BURST PHASE RV2 so that the burst "pulse" in the R-Y chroma is the same amplitude (opposite polarity) as the burst "pulse" in the B-Y chroma signal.

Burst amplitude should then be 0.3v p-p - the same amplitude as syncs

Mon/TV. Most domestic TVs will tolerate -50% to +200% variation in burst amplitude so the setting is not critical.

R26 in the R-Y matrix will alter burst amplitude and should this require changing in value to achieve correct operation then RV2 will require re-adjustment.

Whilst the input of the red, green and blue signals is matched to 75 ohms nominal which should prove to be sufficiently accurate, an exact match may be obtained by selecting resistors R84, R85 and R86 if desired.

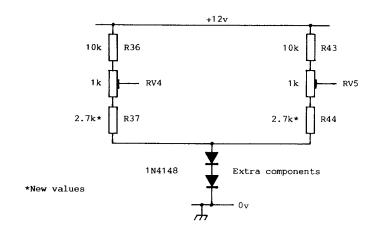

#### ADDENDUM.

Since this circuit first appeared in BATC Handbook-1, Brian Wade G8ABD devised a simple modification which was found to be beneficial in improving temperature stability. Modification involves lifting the earthy end of R37 and R44 and returning them to ground via 2 series 1N4148 diodes as indicated below. R37 and R44 should also have their values changed to 2K7. A further improvement in sub-carrier streaking after the test card red and white bars can be effected by increasing the value of C7 to 1uF.

## CHAPTER 3 SECAM CODER

INTRODUCTION

by Jacques Pochet, F6BQP

The coder described below enables you to produce from the three primary signals red, green and blue together with synchronising pulses and a half-line rate switching signal, a composite SECAM colour signal. The details of this signal are as follows:

In colour television we distinguish two sorts of video signal, the luminance signal, called Y (which corresponds to a black and white signal), and the chrominance signals.

The luminance signal is defined by the fundamental colour weighting

equation: Y = 0.299R + 0.587G + 0.114B.

The chrominance signals are the colour difference signals B-Y and R-Y. The Y signal is transmitted as a classic black and white signal, while the B-Y and R-Y signals are in the form of a subcarrier modulated in frequency and situated at the top of the video spectrum towards 4.43 MHz. This is the basic principle which makes colour transmissions compatible with black and white ones.

Starting with these Y, R-Y and B-Y signals the receiver must retrieve the three primaries, R G and B. In the SECAM system the subcarrier is modulated alternately one line after the other by the B-Y and the -(R-Y) signal. The original or resting frequency of the subcarrier for the B-Y is FoB = 4250 kHz and for the -(R-Y) FoR = 4406 kHz.

To limit interference between the luminance and chrominance signals it is arranged that the instantaneous frequency of the subcarrier should not exceed 3900 and 4756 kHz. The maximum excursion thus for FoB is  $-350\ \text{to}$  +506 and .for FoR -506 to +350 kHz. Nominal excursion (for 75% saturated colours) is  $+230\ \text{kHz}$  for FoB and  $+-280\ \text{kHz}$  for FoR. The chroma passband is limited to 1.4 MHz at -3dB (the Y signal retains all the necessary passband to transmit fine details of the picture).

Apart from this, the chroma signals undergo a preemphasis (the maximum of this is +8.5 dB at 750 kHz) to avoid high frequency components being lost in transmission noise. Before being incorporated in the luminance spectrum the subcarrier signal passes through an "anti-cloche" correction circuit, which is a notch filter centred on 4286 kHz and which has the effect of turning up the extreme side bands of the modulation. Inside the receiver the cloche (bell-shaped) curve restores proper amplitudes.

Finally, and this is only for older TV sets, nine identification lines are introduced into the vertical blanking interval, the frequency of the subcarrier during these lines being alternately 3900 and 4756 kHz. This allows the receiver to pinpoint the correct chroma senses. However, all TV sets made during the last three years function with line ident only and for these the frame ident is no longer necessary.

In professional coders the rest frequencies of the subcarriers are locked to the line frequency: FoB =  $272 \times fH$  and FoR =  $282 \times fH$ . The circuit shown

here uses a free running oscillator (multivibrator) but thanks to a certain number of precautions the stability obtained is sufficient for use under normal conditions. In order to trace chroma signals easily on an oscilloscope we use a normalised colour bar signal. The preemphasis provokes some ballistic shift, the amplitude of this being limited by clippers.

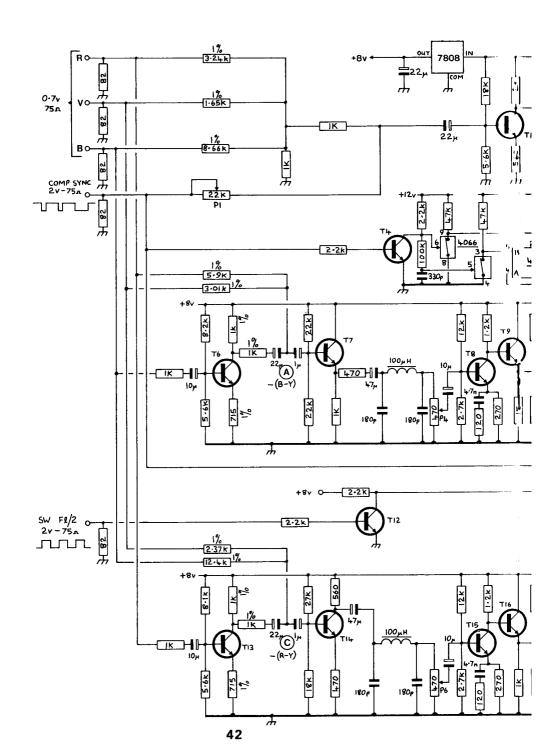

#### PRINCIPLE OF OPERATION OF THE CODER

The three signals RGB are added in a resistive mixer to form the luminance signal Y. The B signal is inverted by TR6 and added to the R and G signals to form the -(B-Y) signal. TR7 is an impedance matcher which leads to the low pass filter composed of 100uH and two 180 pF (matched to 500 ohm) which limits the chroma pass band. TR8 inverts the signal and achieves the preemphasis with its emitter decoupling. At the emitter of TR9 we have the B-Y signal at low impedance. This signal is clamped by TR10 to a fixed potential fixed by potentiometer

P5. It is this voltage which determines the rest frequency of the subcarrier oscillator.

The -(R-Y) is formed in the same way, with an additional phase inversion carried out by TR14.

The B-Y and -(R-Y) signals are then changed over on each line by a 4053 analogue switch and modulate the subcarrier oscillator made up of a multivibrator (TR23 and TR24). The chroma signal is then limited in amplitude by the clipper: TR20 prevents the signal from exceeding a threshold set by P8 and TR21 stops the signal from falling below a level set by P9. The two other 4053 analogue switches enable insertion in the vertical interval in the following manner: the combined sync pulses available at the collector of TR4 are integrated by the 100 Kohm and the 330 pF which allows the field syncs to be picked off, and after shaping by one of the 4066 analogue switches trigger two monostables in cascade (4528). The second monostable, with a period of 576 uS, defines the length of the nine ident lines inserted; during this time and thanks to the 4053 switch the chroma signal is replaced by two continuous voltage levels which make the clipper go high or low to give 4756 or 3900 kHz.

The subcarrier signal, frequency modulated, goes through a low pass filter to attenuate its harmonics, then undergoes the anti-cloche filter. It is amplified by TR5 and is passed to the output video amplifier. One gate of the 4066 analogue switch cuts off the subcarrier during sync pulses.

The treatment of the chroma takes a finite time and it is necessary to retard the Y signal to the same extent using a delay line. This should be in the order of 400 to 600 nS and could be found in an old junked TV set.

#### REMARKS

1. With the simplified type of video/sync mixer used here it is essential that the RGB signals are "clean", i.e. no signal during line and field blanking.

- 2. The base emitter junctions of TR19 and TR22 make up a temperature correction for any drift in the subcarrier frequency. This drift, after compensation, is in the order of -1 kHz per degree centigrade. Tests have shown that frequency errors start to cause visible changes of tints on the screen after frequency errors of +- 20 kHz. So if you make your adjustments at 25 degrees the coder should be usable at temperatures between +5 and +45 degrees C. The stability of the control voltages for the oscillator is assured by an 8 volt IC regulator, which is essential to guarantee good frequency stability.

- 3. The sync pulses together with the half line frequency switch are normalised at 2 volts into 75 ohm. TTL signals may be used direct if the 82 ohm terminating resistors are removed.

#### PRACTICAL CONSTRUCTION

Construction is carried out using a double sided printed circuit board with the upper face used as a ground plane. The ground plane is removed around the holes of the components to avoid undesired shorts. Connections to ground are made direct to the upper face of the board without holes. Integrated circuits are placed in sockets.

The 3.9 and 100 uH inductances are non adjustable moulded coils (e.g. Orega). The coils in the anti-cloche circuit should be adjustable and can be made up as follows:

1.9  $\,\mathrm{uH}=15$  close turns of 0.3 mm enamelled wire on a 7 mm former with adjusting slug.

$3.8\,$  uH  $^{\circ}=\,22\,$  close turns of 0.2 mm enamelled wire on a 7 mm former with adjusting slug.

#### SETTING UP

1. Adjust video and sync levels.

Remove the 4066 from its socket (to suppress the subcarrier). Terminate the video output in 75 ohm and connect the scope there. Inject 0.7 Vpp (pp = peak to peak) signals into R G and B. Adjust P2 to have 0.7 Vpp of video amplitude at the output (not counting the sync pulses). Now adjust P1 to get 0.3 V of sync, so as to have a composite video signal of 1 Vpp amplitude.

2. Verify white balance.

Link RGB together and inject a low frequency signal (e.g. 10 kHz) of 0.7 Vpp amplitude (note that the terminating resistance is only 25 ohm here). Check with the scope that at points A and C that the amplitude of the signal is less than 10 mVpp. If not, adjust the emitter resistors of TR6 and TR13 to obtain minimum voltage. If you have used 1% resistors there should be no adjustments to make.

3. Set rest frequencies for FoB and FoR. Connect a digital frequency counter to the point marked "Test Fo". Adjust F8 so that the rotor is at the +8 V end and P9 is at the earthy end (with the clipper out of service). Take out the 4053 from its socket and inject a continuous voltage at the base of TR19. Adjust CV1 to obtain the following voltage /frequency combinations\*

| Voltage on                        | TR19 base | Frequency                                    |

|-----------------------------------|-----------|----------------------------------------------|

| 2.7 V<br>3.25 V<br>3.5 V<br>4.0 V |           | 3900 kHz<br>4250 kHz<br>4406 kHz<br>4756 kHz |

Replace the 4053 in its socket. Leave RGB in mid-air and connect sync pulses. Link pin 5 of the 4066 for the time being to ground in order to suppres the field ident lines (or remove the 4066 from its socket). Tie SW to ground and ajust P5 to obtain 4250 kHz. Tie SW to  $\pm$ 2 V and adjust P7 to obtain 4756 kHz.

- 4. Setting clipping levels and field ident lines. Remove the 4053 from its socket. Link pin 4 of the 4053 socket to pin 1, then adjust P9 to obtain 3900 kHz. After this, link pin 4 to pin 13 and adjust P8 to obtain 4756 kHz.

- 5. Adjustment of anti-cloche circuit and subcarrier leve!. Having taken the 4053 out of its socket, connect a voltage to the base of TR19 so as to obtain 4286 kHz. Connect the oscilloscope to the base of TR5. Now adjust L1 and L2 for the smallest peak to peak voltage on the scope. This should be about 80 mVpp. Still with 4286 kHz, adjust P3 to obtain 160 mVpp of subcarrier at the video output.

- 6. Setting the frequency excursions. This adjustment should be carried out with the aid of a colour bar pattern which you inject as RGB. For 525 mVpp signals (75% bars) adjust P4 to obtain 700 mVpp at the emitter of TR9 and adjust P6 to obtain 850 mVpp at the emitter of TR16.

Note: when making peak to peak measurements of chroma signal amplitudes pay no attention to over voltages caused by the preemphasis.

## BATC MEMBERS SERVICES:

Peter Delaney, G8KZG 6 East View Close, Wargrave, Berks. RG10 8BJ

## CHAPTER 4 THE HOME COMPUTER

There is no doubt that the personal home computer is making great inroads into Amateur Television. Computer generated graphics can be seen on the airwaves, serial numbers and callsigns are displayed using computer generated graphics and contest points, distance between QRAs or QTHs are often calculated by means of a home computer as are beam headings. Even our club magazine CQ-TV is now computer processed.

In this chapter we shall be looking at how one of the most popular home computers, the Sinclair Spectrum, works, how to build specialist hardware and specific programs that make it suitable for Amateur Television applications. We will also be looking at amateur television programs for the BBC home computer.

If at the moment you do not own a home computer and are thinking of investing, the Sinclair Spectrum is an ideal starting point. Don't be put off by the admittedly inferior keyboard: many manufacturers make keyboards that are a direct plug in replacements which add that "up market" touch.

The Sinclair Spectrum also operates on 9 volts with internal inverters providing negative and +12 rails so it is ideal for portable operation. While on the subject of the inverter TR4 (ZTX651) is a little prone to failure, so check the -5 volts across C47 if you have any problems. Replacing TR4 with a BFY52 seems to fix any future recurrence.

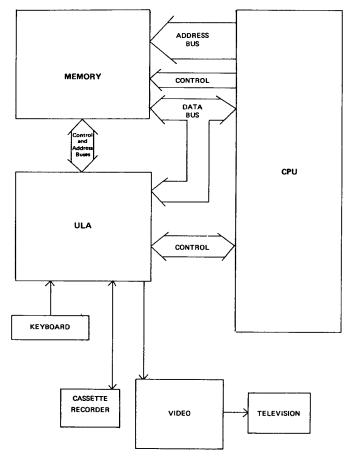

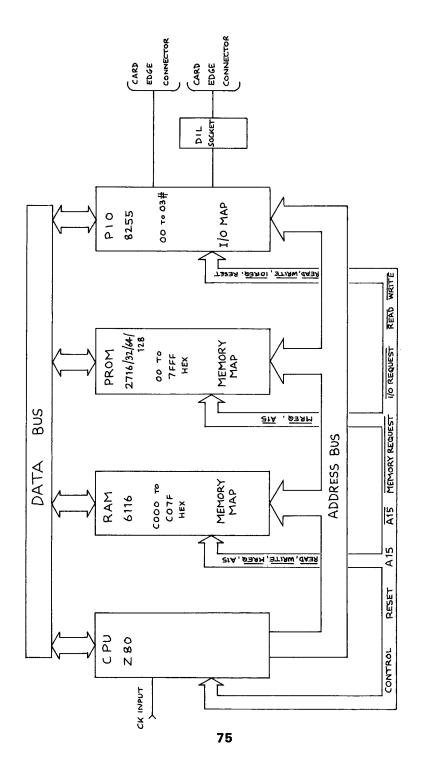

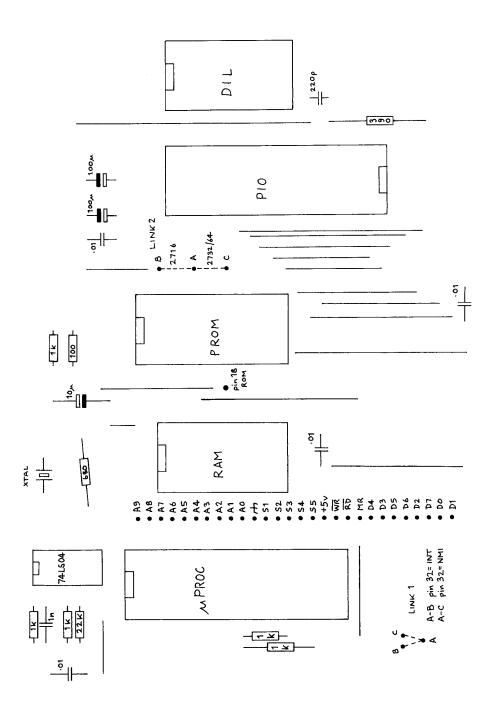

Fig.1 shows the block diagram of the Spectrum. The CPU (central processing unit) is a Z80A which is an 8 bit CPU. This means there are 8 separate connections to its data bus. The CPU can send information to other devices in the Spectrum along this databus and other devices can send data back to the CPU along this same data bus. Because there are eight connections, each one of which can be either a logic 0 or a logic 1, any number between 0 (all zeros) and 255 (all ones) can be sent via the data bus.

Before the CPU can start doing anything it must be instructed what to do. The instructions for running BASIC are held in memory. The BASIC operating system is written in machine code and stored in the memory. The memory is made up both of RAM (random access memory) which is volatile (it forgets when power is removed) and ROM (read only memory), which does not forget when power is removed but can not be written into by the computer. The BASIC operating system is stored in the ROM part of the memory.

Once the program has told the computer what to do the CPU must get its inputs from the keyboard or cassette. The ULA helps the CPU interface with the outside world: the cassette interface circuits are in here along with the TV sync pulse generator and character generator. ULA stands for uncommited logic array and is a Ferranti chip containing a large number of

unconnected logic gates. It can then be customised to form any circuit configuration required. In this case it is customised to a circuit designed by Sinclair and houses almost all the circuitry of the microcomputer with the exception of CPU and memory.

Fig.1 SPECTRUM BLOCK DIAGRAM

The keyboard is interrupt-driven which means 50 times per second the ULA interrupts the CPU so it stops doing whatever it is doing and lodges the current task in a part of memory known as the stack. It then services the keyboard scanning routine to see which push button has been pressed and responds accordingly. When the keyboard has been serviced the CPU returns to the stack, picks up its old job and resumes this until the next interrupt.

When data is being transferred by the CPU various control signals are generated: for example RD is generated when the CPU wishes to read data. WR is generated when the CPU wishes to write data into memory or IO (input/output).

An address is also generated by the CPU when executing memory read or write so as to indicate where in memory it wishes to read or write. The Z80A address bus has 16 bits, i.e. it can support 65,536 memory locations.

Both the memory buses and the data buses are digital meaning they can only carry ones and zeros, where logic zero is a condition between 0 and 0.8V and a logic 1 is a condition between 2 and 5 volts.

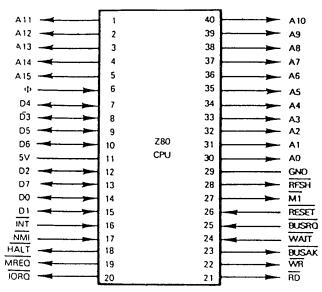

There is much specialist information available on the Z80A micro and in this limited space a drawing of the pin base and a description of pins other than address and data (which we have already covered) will have to suffice.

Pin 6 CLOCK input. On this pin we feed the Z80A with its clock - unlike some micros a complex clock is unnecessary and a simple crystal oscillator up to 3.5MHz will suffice. The only criteria are that its transitions must be fast and a 50/50 mark/space ratio must be maintained for high speed operation.

Pin 16 INT Interrupt request. This pin is active low and is an input to the Z80 to stop it executing its current task, lodge that task in stack and run a special machine code routine in memory. In the case of the Spectrum the keyboard is serviced in this way.

Pin 17 NMI Non maskable interrupt. Again this is an active low input to the Z80; when activated the micro will jump to memory location 102 (66HEX) and execute the programme there (re-initialise Basic in the case of the Spectrum).

Pin 18 HALT. This pin is an output of the Z80 and goes low when the CPU has executed a software halt.

Pin 19 MREQ. An active low output that signals that the address bus now contains a valid memory address which can be read or written to.

Pin 20 IORQ Input/Output Request. Active low and indicates that the address bus AO to A7 holds a valid I/O address.

Pin 21 RD. Active low and indicates that the CPU wishes to read from memory or  ${\rm I/O}$ .

Pin 22 WR. Active low and indicates that the CPU wishes to write to  $% \left( 1\right) =1$  memory or 1/0 .

Pin 23 BUSACK. Active low and works with BUSREQ, pin 25, in that external devices requiring exclusive use of the data and address buses can request this by pulling pin 25 low. The micro signals back you have the bus by putting pin 23 low.

Pin 24 WAIT. Active low input to the CPU used by slow memory to tell the CPU they are not yet ready.

Pin 26 RESET. This input forces the CPU to reset state. In the Spectrum C27 holds the reset low until it has charged by R41. This allows the rest of the computer to reach an operational state before the CPU starts to run the program from address zero.

Pin 27 M1. Machine cycle 1. This output goes low to signal that the computer is currently getting the OP code for the next instruction to be executed from memory.

Pin 28 RFSH. Active low output which indicates that the address bus AO to A7 contains refresh addresses for dynamic memories. All RAM memory can be divided into two types, static and dynamic. Static works by setting or clearing a flip flop depending whether we wish to store a logic 1 or a logic O. Dynamic RAM works by charging or discharging a capacitor, but as capacitors will not hold a charge indefinitely then some system of replacing that charge must exist ie refresh. All 16k RAM is dynamic and the extension RAM is pseudo-static, i.e. dynamic with its own on-chip refresh.

Having now digested a little on the theoretical side of  $% \left( 1\right) =1$  our  $\left( 1\right) =1$  our Spectrum let's move on to practical things.

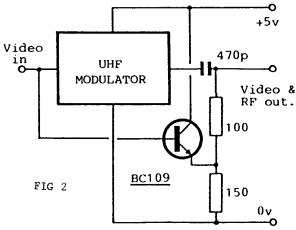

The first use for a Spectrum in our TV station must be as a video generator and the first problem we encounter is that it has no video output, only RF suitable for connecting to a TV set.

Fig. 2 shows how to put all this right. The 20 pF capacitor can be fitted inside the modulator compartment by removing all the connections from the phono socket and fitting the 20 pF capacitor between them and the socket. Use a physically small capacitor so as to create minimum disturbance to the modulator layout. The 75 ohm resistor is also fitted to the phono socket inside the modulator compartment and routed to the outside world through

the spare hole at the connection end of the modulator can. Video input to the modulator is the centre connection on issue 3 Spectrums and +5V is available on the end connection. The transistor can be mounted outside the modulator case by soldering it directly to these connections along with the 330 ohm resistor, which earths to the can. This work will invalidate your

guarantee but by exercising a little care the process could be reversed and leave no traces behind if your Spectrum should need to be repaired under guarantee.

The phono socket now carries both RF at channel 38 and video which is suitable for driving a TV monitor directly. The two signals are far enough apart in frequency not to cause any mutual problems when sharing the same socket.

The video the Spectrum generates does leave a little to be desired in that its frame sync is a simple slab pulse devoid of any broad pulses and lacking proper interlace. The line waveform is fine, in fact better than the more expensive BBC computer in that the burst is positioned correctly on the back porch. The PAL coder is better (an LM1889, see Handbook 2) as opposed to a discrete TTL switching system in the BBC.

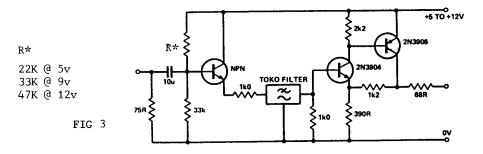

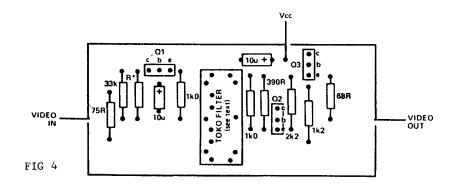

Before we let loose the video from our Spectrum or any other computer on the airwaves a good low pass video filter is recommended. Fig. 3 shows the circuit of a good low pass video filter. It is based on the TOKO low pass linear phase video filter. The circuit will function on a variety of different voltage power supplies simply by changing the value of a resistor to set the operating point of our first transistor. The TOKO filter unit is available from Cirkit (formerly Ambit) and is a 23LVS1110 which has a bandwidth of 4.5 MHz at its 3 dB points. Where video bandwidth can be restricted further, in such times as contests and in areas of high television activity, the 23LVS1109 filter should be used. This filter has a bandwidth of 2.3MHz at its 3dB points. A printed circuit board is available for this project. Fig. 4 shows the component layout.

Now we have our computer generating video the next problem we come to is the size of the characters. The characters are quite readable on the shack monitor, but not all ATV contacts are made over a noise-free path. To increase the size of your characters simply type in program 1.

```

10 RUN 9020

100 FOR Y=0 TO 179 STEP 36

110 FOR X=0 TO 255 STEP 32

120 PAUSE 0: BEEP .05,32

125 LET P=PEEK 23560

130 IF P=12 THEN RUN 100

140 GO SUB 8000: NEXT X: NEXT Y

150 INPUT LINE A$: RUN 100

8000 LET W=4: LET H=4

8810 POKE 23297,175-Y

8820 POKE 23298,W: POKE 23299,H

8830 LET C=15360+8*P: LET D=256

8840 POKE 23548, C-D*INT (C/D)

8845 POKE 23549, INT (C/D)

8850 POKE 23296,X

8860 LET L=USR 65000: RETURN

8865 DATA 42,141,92,34,143,92

8870 DATA 237,75,0,91,237,67,176

8880 DATA 92,237,67,254,91,6,8

8890 DATA 197,42,252,91,126,50

```

8900 DATA 129,92,35,34,252,91 8910 DATA 237,75,2,91,197,58,129 8920 DATA 92,6,8,197,203,23,237 8930 DATA 75,1,91,197,48,15,229 8940 DATA 213,245,237,75,176,92 8950 DATA 197,205,229,34,193,241 8960 DATA 209,225,237,75,176,92 8970 DATA 12,237,67,176,92,193 8980 DATA 16,226,193,16,216,237 8990 DATA 75,254,91,5,237,67,176 9000 DATA 92,237,67,254,91,193 9010 DATA 16,194,193,16,175,201 9020 CLEAR 64999: LET B=0 9030 FOR F=65000 TO 65101 9040 READ A: POKE F,A 9050 LET B=B+PEEK F 9060 NEXT F: BEEP .1,20 9080 IF B=13250 THEN GO TO 100 9090 PRINT "ERROR"

#### Program 1 GENERATE LARGE CHARACTERS.

```

1000 DATA 17,0,61,33,0,250,6

1010 DATA 96,197,6,4,26,119,35

1020 DATA 119,35,19,16,248,19

1030 DATA 19,19,19,193,16,238

1040 DATA 17,0,61,6,96,197,19

1050 DATA 19,19,19,6,4,26,119

1060 DATA 35,119,35,19,16,248

1070 DATA 193,16,238,201

1080 CLEAR 63949: LET Y=10

1090 FOR F=63950 TO 63999

1100 READ A: POKE F,A: NEXT F

1110 RANDOMIZE USR 63950

1120 DIM A$(45): INPUT LINE A$

1130 POKE 23607,249

1140 PRINT AT Y,0;A$( TO 32)

1150 POKE 23607,252

1160 PRINT AT. Y+1,0; A$( TO 32)

1170 LET A$=A$(2 TO )+a$(1)

1180 IF CODE INKEY£=32 THEN GO TO 1200

1190 PAUSE 10: GO TO 1130

1200 POKE 23607,60

```

## Program 3 DOUBLE HEIGHT, SCROLLING CHARACTERS. (Merge with program 1)

If you type in an error in the data statement then 'Error' will be printed at the end. If all is OK a beep will be heard and then you are ready to type. The screen size is 8 characters wide by 5 lines deep. If you wish to use the machine code routine to use letters of a different size then adjust the variables X and Y for the X and Y co-ordinates on the screen. The variable W is width of the characters and H the height.

The delete function is used to clear the screen. If your computer is the BBC then the following program will give you a similar effect.

```

10 MODE 5

20 YS%=18:YS%=22

30 ON ERROR RUN

40 FOR Y%=1000 TO 200 STEP -200

50 FOR X%=100 TO 1220 STEP 160

60 A$=GET$:IF ASC(A$)<32 THEN 60

70 B=&CO00+(ASCA$**8)-256

80 GOSUB 100:NEXT:NEXT

90 INPUT TAB(0,31)A:RUN

100 YY%=Y%:FOR G=0 TO 7

110 A=?B:XX%=X%:FOR F= 0 TO 7

120 IF A/2<>INT(A/2) THEN GOSUB 150

130 A=INT(A/2):XX%=XX%-XS%:NEXT

140 B=B+1:YY%=YY%-YS%:NEXT:RETURN

150 PLOT 4,XX%,YY%:PLOT 1,XS%,0

```

160 PLOT 81,0,-YS%:PLOT 1,-XS%,0

170 PLOT **81,0,YS%:**RETURN

Program 2

Program 3 enables your Spectrum to print double height characters which scroll across the screen in billboard fashion. The maximum length is 45 characters but this could be increased by changing the number in the DIM statement line 1120. The variable Y controls the position on the screen and can be any number from 0 to 20. To stop the routine simply press the space bar. If you accidentally break out of the program you may find the listing consists of strange looking characters. To get back to normal type GOTO 1200.

# SPECTRUM USER PORT PROJECT

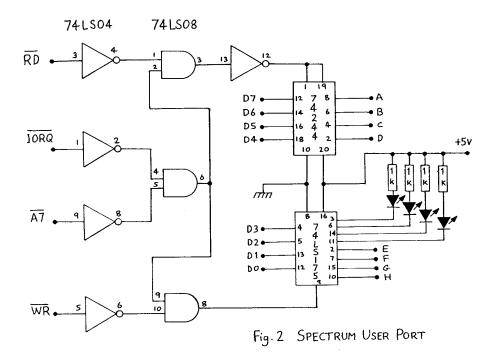

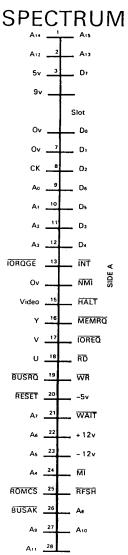

Having now mastered using the Spectrum as a video source we can turn our attention to using it in control applications. Fig.1 shows the rear edge connector of the Spectrum which carries the data, address, and control signals to and from the Z80 micro. Pin 17 is the IOREQ; this pin is active low whenever the Spectrum is doing an input, output operation (input output request). This statement is not strictly true because Sinclair does use an IOREQ to do some functions within the computer. The AO to A7 pins carry address information which means we can in theory access 255 I/O locations by decoding this part of the address, bus. Sinclair use AO to address the ULA, A1 Sinclair Printer, and A2 A3 A4 to control the Micro Drive, leaving A5 A6 A7 free for us to experiment with.

A7 along with  $\overline{\text{IOREQ}}$  go low under the BASIC command  $\overline{\text{IN}}$  127 or OUT 127, depending whether we wish to receive or send data.  $\overline{\text{RD}}$  will accompany the IORQ and A7 in going low on the BASIC command IN 127 and  $\overline{\text{WR}}$  will accompany the  $\overline{\text{IORQ}}$  and A7 in assuming a low under the BASIC command OUT 127. By use of TTL logic as per Fig.2 we can decode these commands and construct a simple user port.

When IOREQ A7 and  $\overline{W}R$  are all low the 74LS175 quad latch is enabled. The D inputs are supplied with D0, D1, D2, D4 so whatever is on the lower part of the data bus when we enable the latch, i.e. IOREQ A7 and  $\overline{W}R$  all going low will be latched and displayed on the LEDs and will also be available to the outside world as TTL commands on pins E, F, G, H, (Fig.2).

```

OUT 127,0 will turn all LEDs Off

OUT 127,1

OUT 127,2

OUT 127,4

OUT 127,8

```

will control each successive LED and the sum of the digits after the comma being used to switch more than one LED on at once, i.e. OUT 127,12 will switch the last two LEDs on simultaneously.

The next stage after getting the computer to issue commands to the outside world is to be able to send instructions to it. This we do by persuading the  $\overline{\text{RD}}$  pin to go low under the instruction IN 127. This will enable the 74224 tri-state driver chip to connect inputs A B C D to the data bus and thus feed commands into our computer. The following short program will read and display the inputs A B C D on the screen.

```

10 PRINT IN 127

20 PAUSE 50

30 CLS

40 GOTO 10

```

The result should be 255 now: try grounding A B C and D in turn and the 255 will change i.e. grounding B should give 191. We can use this in BASIC by the following

```

5 PAUSE 10

10 IF IN 127 = 191 then GOTO 5

20 BEEP 4,4

30 GOTO 5

```

where a ground on pin B will put 191 on the data bus and keep the computer executing lines 5 and 10, removing the ground will cause line 20 to be executed and the Beep will result.

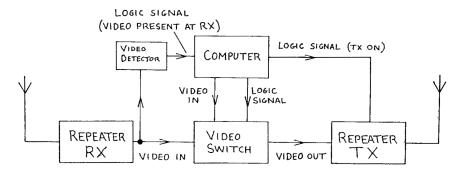

Let's try putting all this new found knowledge to use in ATV and design an ATV repeater. (Block diagram fig.5).

Fig. 5 TV REPEATER - BLOCK DIAGRAM

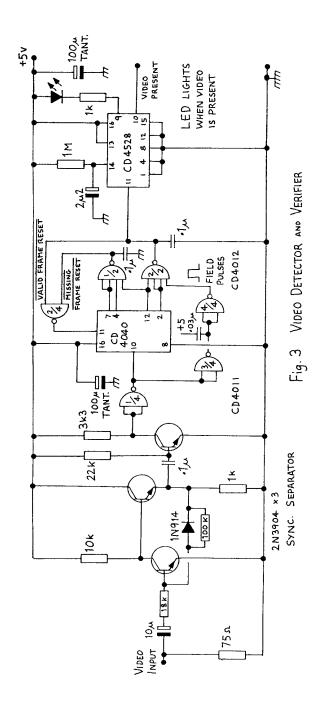

Fig.3 shows a circuit which will produce a logic 1 signal when fed with standard 625 line video signal. If this is fed into input B of our user Port then when video is present the data bus will display 255, and 191 when video is absent.

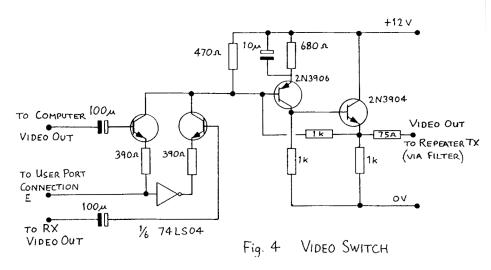

Fig.4 shows a logic-driven video switch which could be connected to E so OUT 127,8 would cause received video or computer video to be fed to the transmitter.

OUT 127,4 could control the transmitter on/off by using pin F to drive a relay which would switch on the transmitter. The following program could be used to drive an ATV repeater.

10 CLS: OUT 127,0: PAUSE 50

20 IF IN 127=191 THEN GO TO 10

30 PRINT "THIS IS GB8ATV"

40 OUT 127,4: PAUSE 200

50 LET X=20

60 IF IN 127=191 THEN GO TO 10

70 OUT 127,12: PAUSE 200

80 LET X=X-1

90 IF X=1 THEN GO SUB 500

100 GO TO 60

500 CLS:PRINT "TIME OUT"

510 OUT 127,4: PAUSE 200

520 OUT 127,0: PAUSE 20

530 IF IN 127=191 THEN RETURN

540 GO TO 520

Fig. 6 Spectrum User Port P.C. Layout

Viewed from front of plug.

## COMPUTER CONTROLLING

## CHARACTER GENERATORS

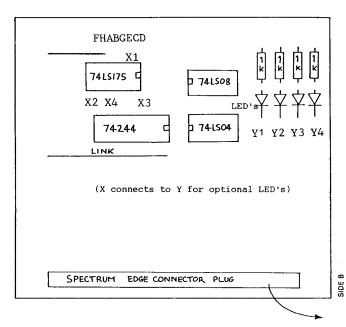

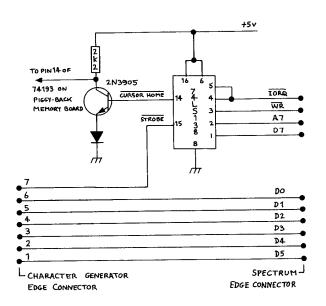

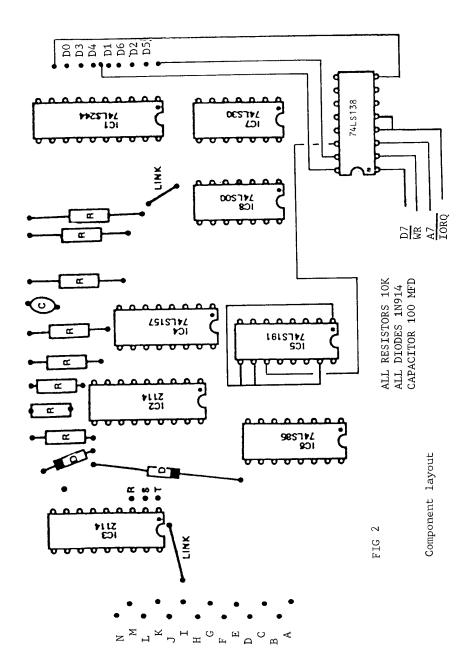

The original BATC character generator, which was based on a R02513 ROM, first appeared in Handbook 1 and required a diode array to set up the characters. In Handbook 2 we added a piggyback memory board which gave keyboard access to the characters. The circuit in Fig.1 shows how to add an interface using only 1 chip which will allow the Spectrum to talk directly to the character generator and piggyback memory. The address used is A7, i.e. out 127, but this could be changed to A6, i.e. out 191. The character generator only requires a 6 bit code to select its characters, leaving data bits 6 and 7 spare. Data bit 7 is decoded in the 74LS138 to form a cursor home control. The decoded command appears from pin 14 of our decode chip and is inverted by TR1; it then goes to pin 14 of the 74193 on our piggyback board. The 150 ohm resistor which holds pin 14 down to ground requires removing. The BASIC command out 127,254 will set the cursor to the home position. The BASIC commands out 127,0 to out 127,64 will cause different characters to be printed: try experimenting by entering these commands in the immediate mode (i.e. no line number, just the command and then enter).

The following BASIC program will enable the character generator to be controlled by the computer keyboard. The characters produced will be upper case; the capshift does not require to be depressed so as to keep the operation as simple as possible. The enter key will home the cursor and bleep for acknowledgement of the command as the cursor is not displayed and so acceptance of this command is not obvious.

```

10 PAUSE 0

20 LET a$=INKEY$

30 LET b=CODE a$

40 IF b=0 THEN GOTO 10

50 IF b=13 THEN LET b=254 : BEEP .1,4: GOTO 70

60 IF b>96 THEN LET b=b-96

70 OUT 127,b

80 PAUSE 10

100 GOTO 10

```

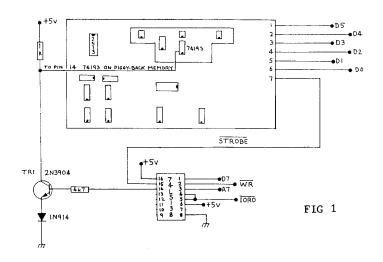

Fig. 2 shows how we can extend this treatment to the new character generator which appears on page 7 of this book. Again a little extra hardware is required but in the case of this generator only a 74LS138, which can easily be mounted as in fig.2 on the keyboard module, by bending out the pins and fixing the chip in place with Superglue. The existing 74LS191 requires pins 1, 9, 10, and 15 joining together and pin 11 routing through to pin 14 of our additional chip (74LS138). Pin 15 of this new chip generates the strobe command which is routed through to the keyboard connector as is +5V and ground. The other pins of the keyboard connector go to the Spectrum data bus as shown. The 74LS138 is also connected to the Spectrum data bit 7, WR, A7 and IORQ.

The keyboard program is a little different this time as the new character generator has lower and upper case characters along with some less useful teletext graphics (128 faces in all).

The enter key is a clear screen as well as a cursor home and the delete key performs the backspace function.

```

10 PAUSE 0

20 LET a$=INKEY$

30 LET b=CODE a$

40 IF b=0 THEN GOTO 10

50 IF b=13 THEN GOTO 1000

60 IF b=12 THEN OUT 127,127: GOTO 10

80 OUT 127,b

90 PAUSE 10

100 GOTO 10

1000 FOR a=1 TO 16

1010 OUT 127,32

1020 NEXT a

1030 OUT 127,254

1040 GOTO 10

```

These two programs show how once the computer is interfaced to the character generator it can double as a keyboard. But doubling as a keyboard is only one of its uses, it could be programed to animate your callsign around the character locations, or even keep time and display the hours, minutes or even seconds via the character generator. It's all down to your imagination and programming skills.

```

10 LET a=22528

15 FOR C=1 TO 104

20 READ b

25 POKE a+b,8

30 NEXT c

40 FOR d=22528 TO 23296

45 IF PEEK d<>8 THEN POKE d,48

50 NEXT d

55 BORDER 6

60 PAUSE 0

65 DATA 11,14,17,44,46,48,77,78,

79,105,106,107,108,109,110,111,

112,113,114,115,137,147,170,178,

203,209,236,240,268,272,300,304,

332,336,364,368,396,400,417,418,

419,423,424,428,432,436,437,438,

439,440,444,445,446,449,452,454,

457,460,464,470,475,481,482,483,

486,489,492,496,502,507,513,516,

518,519,520,521,524,528,534,539,

545,546,547,550,553,557,558,559,